pn结的电容效应 为什么在pn结间加入i层可以减小结电容? PN结是一种半导体器件,其中P型半导体和N型半导体间由弱耗尽区隔离。这种器件有许多应用,例如光电探测器、太阳

2023-10-19 16:42

对于高速TIA的PCB来说,最大的挑战就是如何减小杂散电容Cstray了** 。这是为什么呢?假如带宽很高,增益很高,那么Cf可能需要设置在如0.5pF,而普通贴片电阻的杂散电

2023-11-01 10:59

首先如果是磁芯导体,应该先减小绕组与磁芯之间的电容,具体方法是在绕组与磁芯之间加一层介电常数较低的绝缘材料,增加绕组与磁芯之间的距离。其次要减小匝间的

2018-01-31 11:39

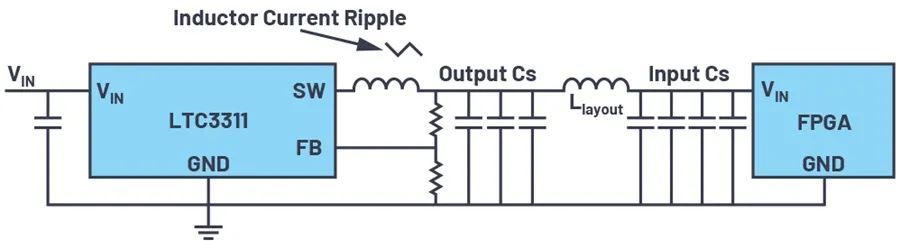

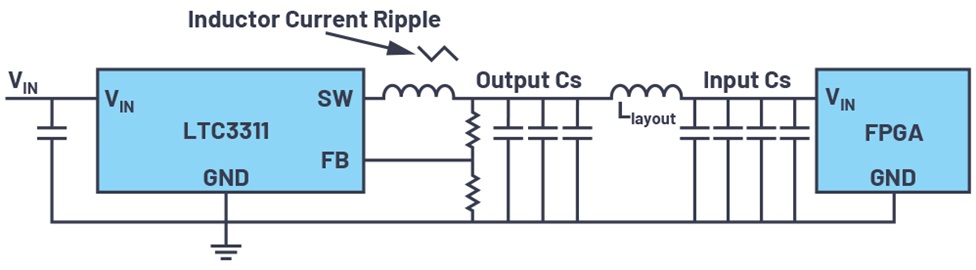

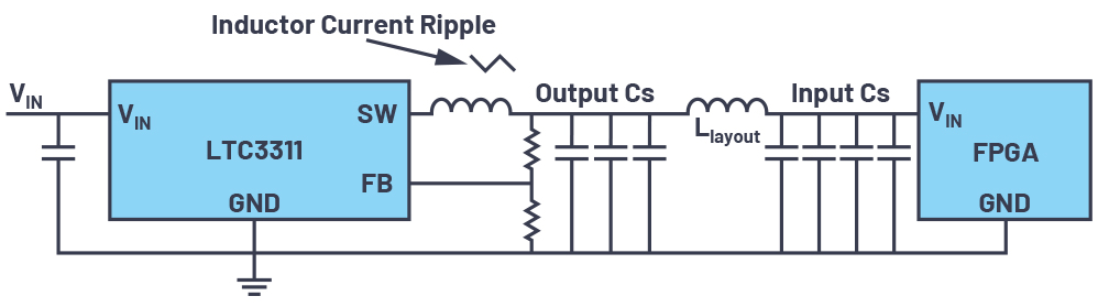

如何最大限度减小电源设计中输出电容的数量和尺寸?

2023-12-15 09:47

半径。大多数资料中都会提到电容摆放要尽量靠近芯片,多数资料都是从减小回路电感的角度来谈这个摆放距离问题。 PCB设计为什么电容要就近摆放 确实,

2023-10-20 09:17

电容器的极间场强是指电容器内部两个极板之间的电场强度。它是由电容器的工作电压和电容器的极板间距决定的。

2024-08-21 14:19

电源输出电容一般是100 nF至100 μF的陶瓷电容,它们耗费资金,占用空间,而且,在遇到交付瓶颈的时候还会难以获得。所以,如何最大限度减小输出电容的数量和尺寸,这个

2023-06-16 10:25

电源输出电容一般是100 nF至100 μF的陶瓷电容,它们耗费资金,占用空间,而且,在遇到交付瓶颈的时候还会难以获得。所以,如何最大限度减小输出电容的数量和尺寸,这个

2022-03-18 11:14

为什么并联电容器后总电流会减小? 并联电容器是电路中常见的元件之一。电容器作为存储电能的元件,在电子电路中扮演着重要的角色。在

2023-09-18 09:50

电路的设计中存在很多 电磁干扰(EMI) 问题, 去耦电容 的应用场景就是减小电磁干扰,这一过程衍生出了另一个概念—— 电磁兼容(EMC) 。

2022-10-21 16:22