优化FPGA(现场可编程门阵列)设计的性能是一个复杂而多维的任务,涉及多个方面和步骤。以下是一些关键的优化策略: 一、明确性能

2024-10-25 09:23

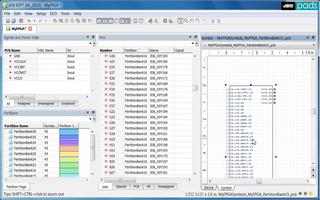

本文主要介绍Vivado布线参数设置,基本设置方式和vivado综合参数设置基本一致,将详细说明如何设置布线参数以优化FPGA设计的性能,以及如何设置Vivado压缩BIT文件。

2023-05-16 16:40

高层次的设计可以让设计以更简洁的方法捕捉,从而让错误更少,调试更轻松。然而,这种方法最受诟病的是对性能的牺牲。在复杂的 FPGA 设计上实现高性能,往往需要手动优化 R

2018-12-16 11:19

现有的工具和技术可帮助您有效地实现时序性能目标。当您的FPGA 设计无法满足时序性能目标时,其原因可能并不明显。解决方案不仅取决于FPGA 实现工具为满足时序要求而

2017-11-18 04:32

FPGA与ASIC的区别 FPGA(现场可编程门阵列)和ASIC(专用集成电路)是两种不同的集成电路技术,它们在多个方面存在显著的区别: FPGA ASIC 基本定义 由通用的逻辑单元组成,可以通过

2024-12-02 09:51

资源、速度和功耗是FPGA设计中的三大关键因素。随着工艺水平的发展和系统性能的提升,低功耗成为一些产品的目标之一。功耗也随之受到越来越多的系统工程师和FPGA工程师的关注。Xilinx新一代开发工具Vivado针对功

2017-11-18 03:11

CPLD(复杂可编程逻辑器件)是一种介于简单PLD(可编程逻辑器件)和FPGA(现场可编程门阵列)之间的可编程逻辑器件。它们通常用于实现中等复杂度的数字电路设计。优化CPLD性能可以通过以下几个方面

2025-01-23 10:03

FPGA I/O 优化功能提供了自动化 FPGA 符号生成流程,该流程与原理图设计和 PCB 设计相集成,可节省大量创建 PCB 设计的时间,同时提高原理图符号的总体质量和准确性。

2019-05-20 06:16

参加 FPGA 功率优化班,将帮助您创建更高电源效率的 FPGA 设计。通过本课程的学习,将有助于您的设计满足更小型化的 FPGA 器件,降低

2017-02-09 06:24

想要机器人实现智能化,需要具有敏锐且优秀的感知,同时还能有精准的运控。就感知计算而言,尤其是视觉以及深度学习,计算量往往很大,对器件性能要求高。而且感知算法也在不断发展,这需要对机器人处理系统做

2022-08-01 07:26