初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数分频、半整

2023-03-29 11:38

最近正在准备找工作,由于是做FPGA开发,所以verilog实现技术分频电路是一道经常出现的题目,三分频,五分频电路等等;经过一下午时间总结出了一个通用电路,可以实现任意奇数分

2017-02-09 14:21

前面分别介绍了偶数和奇数分频(即整数分频),接下来本文介绍小数分频。

2023-03-23 15:08

在数字系统设计中,根据不同的设计需要,经常会遇到偶数分频、奇数分频、半整数分频等,有的还要求等占空比。在基于cpld(复杂可编程逻辑器件)的数字系统设计中,很容易实现由计数器或其级联构成各种形式的偶

2020-06-26 09:36

分频器主要分为偶数分频、奇数分频、半整数分频和小数分频,如果在设计过程中采用参数化设计,就可以随时改变参量以得到不同的

2019-02-01 01:28

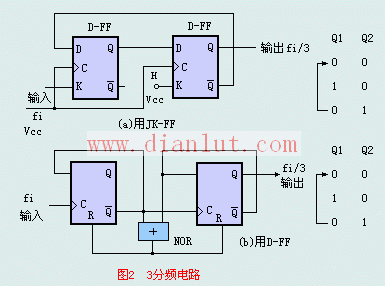

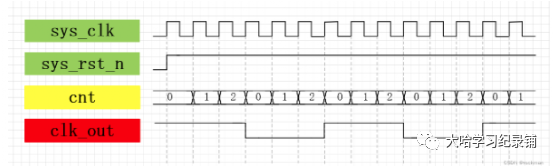

三分频电路,在电路图中,在一般的利用常规计数器对数字脉冲进行奇数分频时,即使输入是对称信号, 输出也得不到占空比为50%的分频输出,其原因是内部触发器采用的是统一的上升沿(或下降沿)进行触发。

2018-08-13 11:08

上一篇文章介绍了偶分频,今天来介绍一下奇数分频器的设计。

2023-03-23 15:06

所谓“分频”,就是把输入信号的频率变成成倍数地低于输入频率的输出信号。数字电路中的分频器主要是分为两种:整数分频和小数分频。其中整

2023-03-23 15:06

通过一个标志信号作为偶6分频的工作时钟(可靠,常用)

2023-10-10 14:23

Σ-Δ小数分频频率合成器相位噪声源到输出端的传递函数除VCO相位噪声传递函数为高通滤波传递函数外,其余噪声源到输出端的传递函数均为低通滤波传递函数。本文着重分析Σ-Δ量化噪声对输出相位噪声的影响。

2018-03-21 08:58