大型设计中FPGA的多时钟设计策略 利用FPGA实现

2009-12-27 13:28

利用FPGA实现大型设计时,可能需要FPGA具有以多个时钟运行的多重数据通路,这种多时钟

2012-05-21 11:26

01、如何决定FPGA中需要什么样的时钟速率 设计中最快的时钟将确定 FPGA 必须能处理的

2020-11-23 13:08

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟

2021-09-23 16:39

减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟

2023-08-23 16:10

在多时钟设计中可能需要进行时钟的切换。由于时钟之间可能存在相位、频率等差异,直接切换时钟可能导致产生glitch。

2020-09-24 11:20

在一个SOC设计中,存在多个、独立的时钟,这已经是一件很平常的事情了。大多数的SOC器件都具有很多个接口,各个接口标准都可能会使用完全不同的时钟频率。

2017-02-11 15:07

把握DCM、PLL、PMCD和MMCM知识是稳健可靠的时钟设计策略的基础。赛灵思在其FPGA中提供了丰富的时钟资源,大多数设计人员在他们的

2023-10-30 11:47

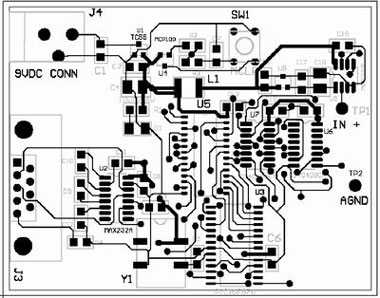

在当今激烈竞争的电池供电市场中,由于成本指标限制,设计人员常常使用双面板。尽管多层板(4层、6层及8层)方案在尺寸、噪声和性能方面具有明显优势,成本压力却促使工程师们重新考虑其布线策略,采用双面板

2023-09-26 09:41

跨时钟域问题(CDC,Clock Domain Crossing )是多时钟设计中的常见现象。在FPGA领域,互动的异步时钟

2019-08-19 14:52