汽车常见EEPROM芯片有哪些? 就汽车上常见的EEPROM芯片按其接口方式来分,无外乎

2010-03-19 10:52

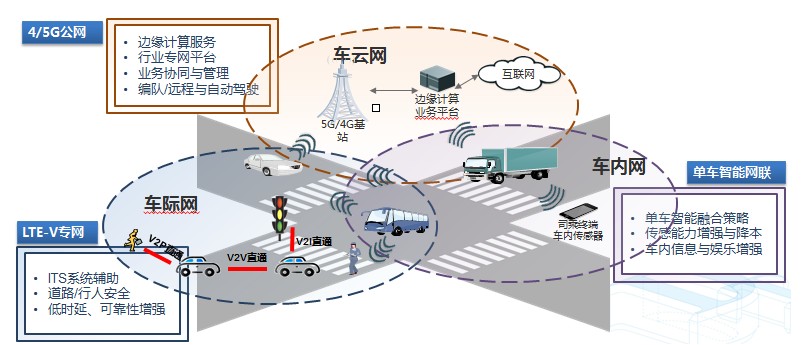

大唐电信集团旗下大唐移动持续致力于超低时延、高可靠性、强安全性等核心关键技术的研究,积极推动V2X在中国乃至全球的产业化进程,促进智慧交通应用的落地开花。

2018-12-29 09:33

当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/CPLD相连接的芯片的工作时钟大多数情形下与FPGA的时钟同源,如果输出的信号经过时钟锁存可以起到如下的作用:

2017-02-11 13:18

II系列器件的一个标准宏单元。虽然不同的厂家的芯片宏单元的结构不同,但概括而言都是由一些组合逻辑外加一或二个触发器而构成。在实际应用中,当一个模块内的组合逻辑被使用了那么与其对应的触发器也就不能用了;同样如果触发器单元被用了那么组合逻辑单元

2017-02-11 13:14

电脑芯片是什么,电脑芯片有哪些,今天我就来为大家简单讲解下电脑芯片含义及其相关组成,供大家阅读参考:

2016-08-09 16:00

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,证设计项目的可靠性变得很困难。

2017-02-11 13:28

汽车产业正在经历前所未有的产业转型,汽车从功能性代步工具逐步演变为智能化移动空间,汽车电子架构也由传统的分布式架构向中央计算平台架构演进。智能汽车对

2023-08-02 17:05

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。

2017-02-11 13:04

国产高端FPGA芯片有多种,以下是一些知名的国产FPGA芯片,

2024-03-15 14:01

异步设计不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

2017-02-11 13:11