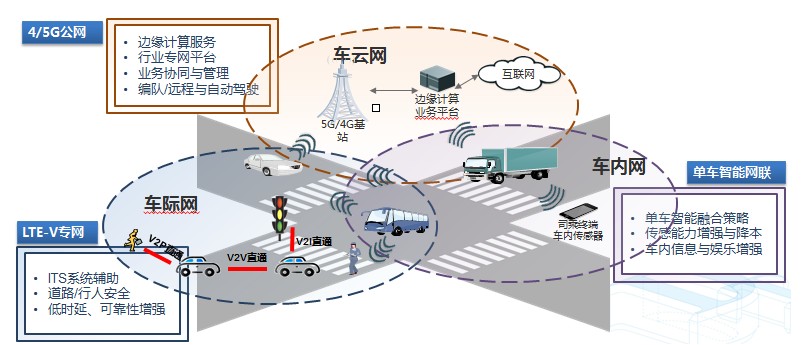

大唐电信集团旗下大唐移动持续致力于超低时延、高可靠性、强安全性等核心关键技术的研究,积极推动V2X在中国乃至全球的产业化进程,促进智慧交通应用的落地开花。

2018-12-29 09:33

注意:当使用多级非门的时候综合器往往会将其优化掉,因为综合器会认为一个信号非两次还是它自己。 需要说明的是在FPGA/CPLD内部结构是一种标准的宏单元,下图是Xilinx公司的Spartans

2017-02-11 13:14

当你需要将FPGA/CPLD内部的信号通过管脚输出给外部相关器件的时候,如果不影响功能最好是将这些信号通过用时钟锁存后输出。因为通常情况下一个板子是工作于一种或两种时钟模式下,与FPGA/CPLD相连接的芯片的工作时钟大多数情形下与FPGA的时钟同源,如果输出的信号经过时钟锁存可以起到如下的作用:

2017-02-11 13:18

当产生门控时钟的组合逻辑超过一级(即超过单个的“与”门或“或”门)时,证设计项目的可靠性变得很困难。

2017-02-11 13:28

从2004年开始,我写过几次小型IC设计中心的IT环境。比较多的论述了创业类型的芯片设计公司,应该怎么去设计自己的IT环境。这10多年间,有不少初创型的公司来咨询过如何更好的规划IT系统,我都尽力协助解决。

2019-03-16 09:34

在数字电路的设计中,时序设计是一个系统性能的主要标志,在高层次设计方法中,对时序控制的抽象度也相应提高,因此在设计中较难把握,但在理解RTL电路时序模型的基础上,采用合理的设计方法在设计复杂数字系统是行之有效的,通过许多设计实例证明采用这种方式可以使电路的后仿真通过率大大提高,并且系统的工作频率可以达到一个较高水平。

2017-02-11 13:04

异步设计不是总能满足(它们所馈送的触发器的)建立和保持时间的要求。因此,异步输入常常会把错误的数据锁存到触发器,或者使触发器进入亚稳定的状态,在该状态下,触发器的输出不能识别为l或0。如果没有正确地处理,亚稳性会导致严重的系统可靠性问题。

2017-02-11 13:11

Maxim公司成立于1983年,总部在美国加州。该公司在设计、发展、生产线性和混合信号集成电路产品方面处于世界领先地位。

2018-04-09 17:07

本文介绍了基于AD574A的脑电信号采集及在线仿真,根据脑电信号的特点,将电极采集到的模拟信号经信号调理后,采用FPGA芯片EP2C8Q208C8来控制AD574A的转换,通过软硬件的设计与实现,并仿真验证,提高系统

2017-12-20 09:33

电信企业计费(Billing)系统是电信支撑系统BSS/OSS 的核心。

2014-08-20 16:47