FPGA(可编程逻辑门阵列)是一种集成电路芯片,具有可编程的数字逻辑功能。多功能数字钟系统利用FPGA技术实现了时钟的显示、计时、报时等

2024-01-02 16:50

本文以FPGA平台为基础,在QuartusⅡ开发环境下设计开发多功能数字钟。数字钟实现计时\校时\整点报时\世界时钟功能.

2012-12-18 11:51

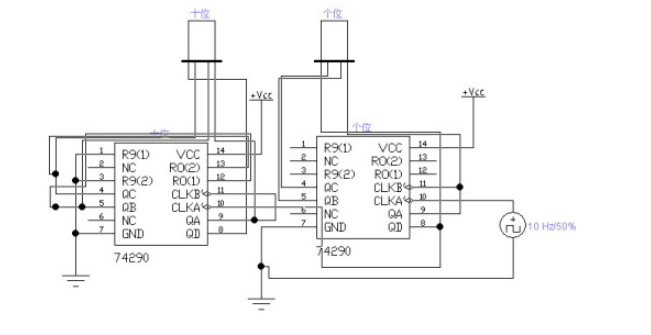

设计说明: 1. 秒钟与分钟显示电路: 分秒显示为60进1,利用两片74290组成的60进制计数器如下图所示,输入计数脉冲CP加在CLKA端,把QA与与CPLB从外部连接起来,电路将对CP按照8421BCD码进行异步加法计数。通过反馈端,控制清零端清零,其中个位接成十进制形式,十位接成六进制形式 2. 时钟显示电路: 本设计采用24小时进制,用两片74290连接成24进制计数器,计数信号由分钟显示电路提供,即当分钟为60时小时计数加一。个位同样接成十进制形式,十位

2020-09-23 14:53

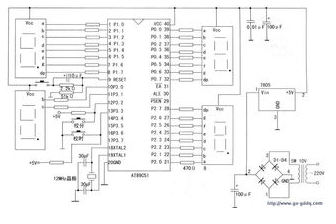

实现原理:利用单片机定时器及计数器产生定时效果通过编程形成数字钟效果,再利用数码管动态扫描显示单片机内部处理的数据。同时通过端口读入当前外部控制状态来改变程序的不同状态,实现不同功能。

2020-01-07 16:28

实现原理:利用单片机定时器及计数器产生定时效果通过编程形成数字钟效果,再利用数码管动态扫描显示单片机内部处理的数据。同时通过端口读入当前外部控制状态来改变程序的不同状态,实现不同功能。

2019-09-24 15:51

以FPGA平台为基础,采用VHDL语言在QuartusⅡ开发环境下设计开发多功能数字钟,具有计时、校时、蜂鸣闹铃的功能.

2017-11-07 12:01

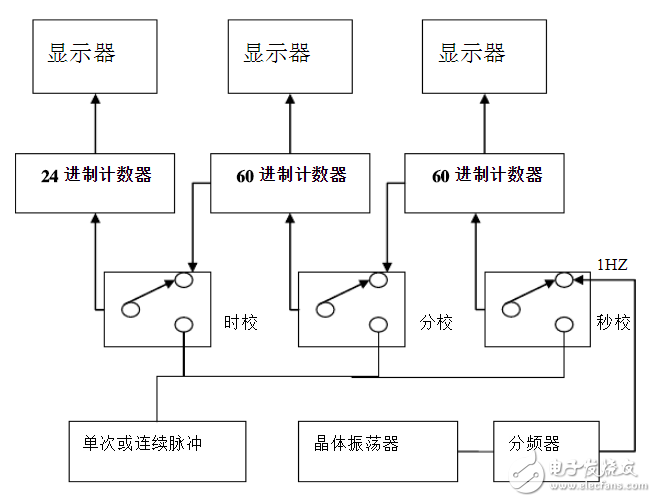

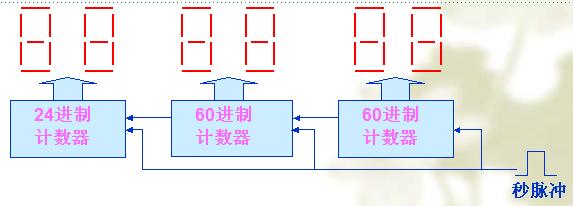

多功能数字钟是一个对标准频率(1HZ)进行计数的计数电路。它由振荡器、分配器、计数器、译码器和显示电路组成。振荡器与分配器组成秒脉冲输出装置,秒脉冲信号输入计数器进行计数,并把累计结果以“时”、“分

2018-01-26 09:52

数字钟原理框图 数字钟系统构成1、数字钟的构成

2008-07-05 12:10

数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定,通常使用石英晶体振荡器电路构成数字钟。

2018-01-15 15:37

数字钟整点报时电路

2011-05-05 17:46