在电子工程领域,复位信号是确保系统稳定、可靠运行的关键因素之一。复位信号通常用于在系统出现故障或异常时,将系统恢复到初始状态,以便重新开始工作。因此,准确测量和分析

2024-05-17 17:14

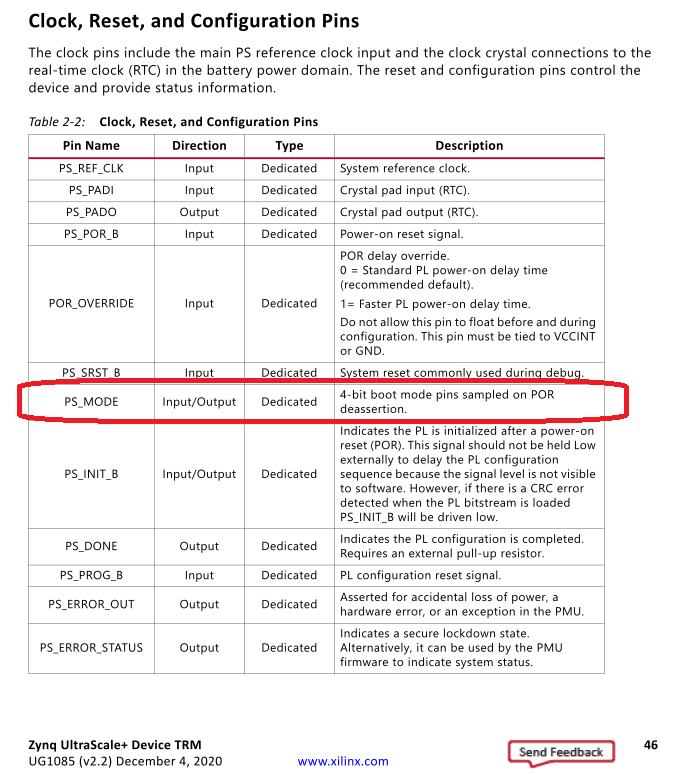

在Xilinx的ZCU102和ZCU106单板设计中,使用了管脚PS_MODE1作为外部USB Phy的复位信号。在MPSoC的文档ug1085和ug1087中,关于PS_MODE1的信息比较少。下面是更详细的描述。

2022-08-02 09:38

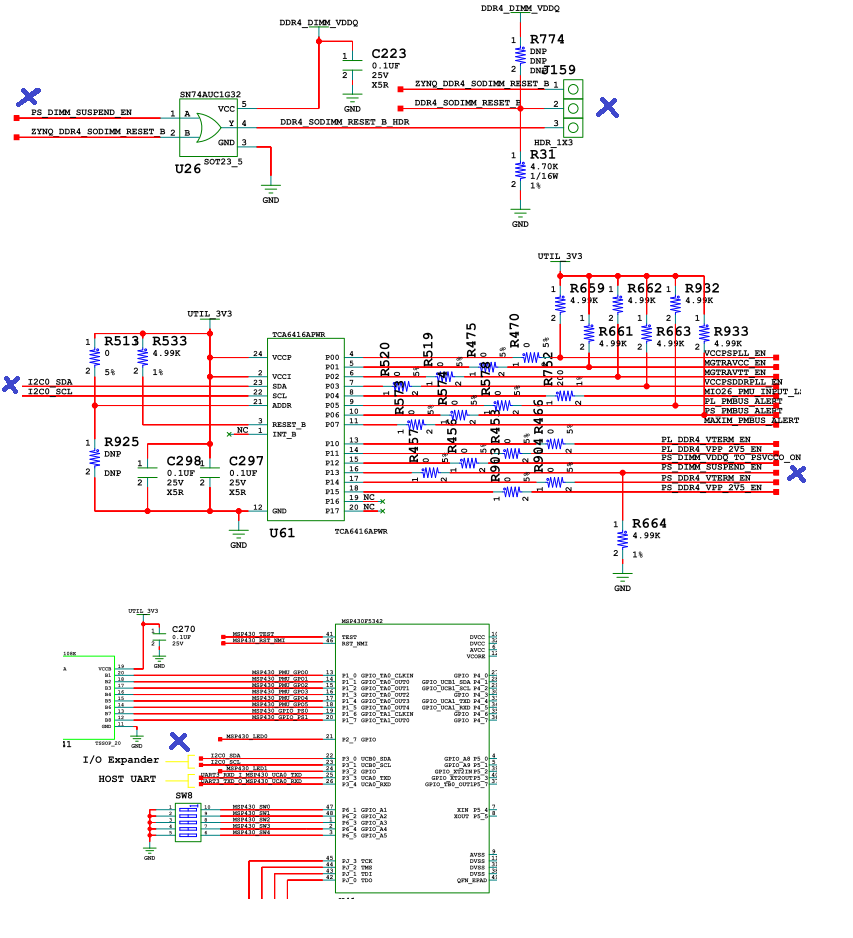

休眠,就从DDR读出系统状态,恢复系统。 MPSoC启动时,它的DDR控制器会驱动DDR的复位信号,有可能破坏DDR里的数据。为了避免这种情况,需要对DDR复位信号进行

2020-11-04 17:02

做了很久FPGA的朋友们,是否有这种经历:一个FPGA设计工程,在研发测试阶段或转产中试阶段发现,FPGA系统在上电运行后,偶尔会有异常现象? 或者说,反复加电测试,有时会出现异常或功能失败的情况。

2017-02-11 14:12

顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。否则,无法完成对系统的复位工作。

2017-02-11 12:40

经常在面试时问到一个问题:对于芯片中的复位信号我们通常会有哪些特殊处理?这个时候我一般希望得到的回答包括:复位消抖、异步复位同步撤离、降频

2023-12-25 09:52

PCI Express 是一种即插即用协议,主机在启动时将枚举 PCIe 设备。此过程包括主机从读取请求中获得每个设备的地址大小,然后为设备分配基地址。因此,PCIe 接口必须在主机查询时准备就绪,否则将不会分配基地址。PCI Express 规范规定,PERST# 必须在系统电源正常后 100 毫秒内解除,并且 PCI Express 端口必须在 PERST# 解除后不超过 20 毫秒内准备好进行 Link training。这通常称为 100 毫秒启动时间要求。

2024-12-04 16:28

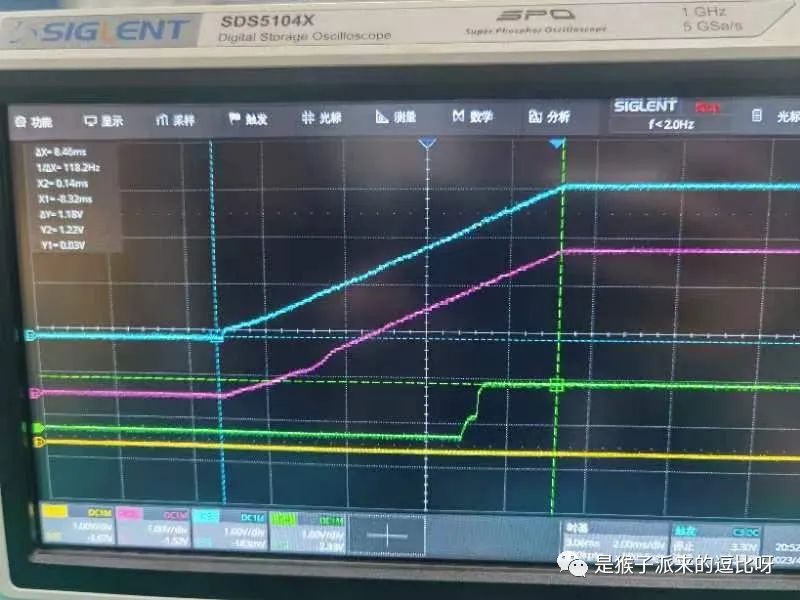

蓝色的是3.3V上电信号(除个别芯片使用其他电压外,整板使用3.3V供电),粉红色的复位信号(此处的复位信号是低电平有效

2023-11-22 15:03

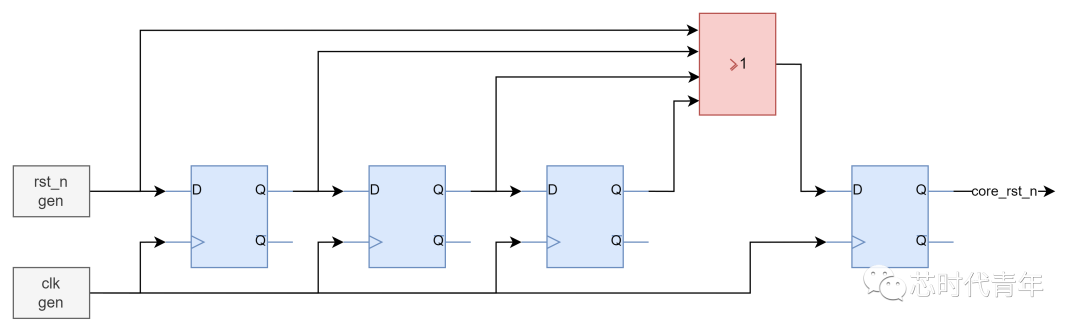

通常情况下,复位信号的异步释放,没有办法保证所有的触发器都能在同一时间内释放。触发器在A时刻接收到复位信号释放是最稳定的,在下一个时钟沿来临被激活,但是如果在C时刻接收

2018-11-19 10:34

异步复位信号a是异步复位信号源,异步复位信号b、c、d是到达触发器的异步

2020-06-26 05:36