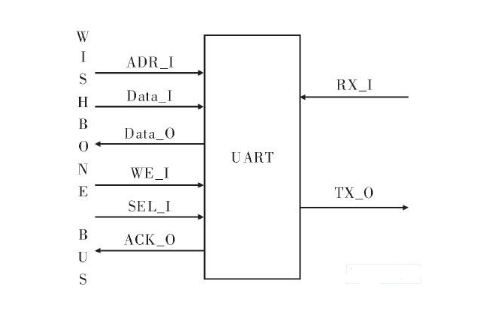

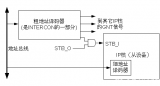

前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示。该从

2018-07-31 09:11

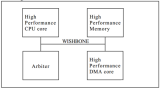

支持用户定义的标签。这些标签可以用于为地址、数据总线提供额外的信息如奇偶校验,为总线周期提供额外的信息如中断向量、缓存控制操作的类型等。Wishbone规范只定义标签的时序,而标签的具体含义用户可自行定义。支持用户定义的标签是Wishbone规范区别与其他片上总线

2018-07-06 08:07

在以上介绍的三种总线中,CoreConnect虽免费不过需要IBM 公司许可,ARM 没有明确的正式说法,可能也会免费,而Wishbone 是绝对免费的。三种总线都是同步的总线,使用时钟上升沿驱图7 8-bit SLAVE输出端口动和采样信号。

2018-08-11 09:14

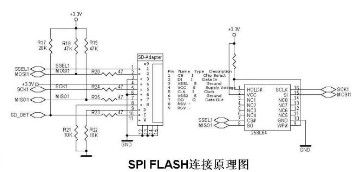

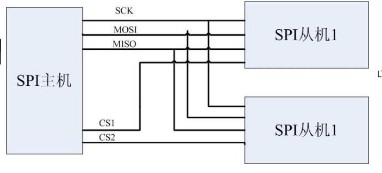

SPI一种通信接口。那么严格的来说SPI Flash是一种使用SPI通信的Flash,即,可能指NOR也可能是NAND。

2018-09-18 14:38

Wishbone部分地址译码的实现如图26所示。对于图中所示IP核,我们假设其只有4个地址,对应4组寄存器。地址译码器首先译码出其地址并给出选择信号,该选择信号与共享总线的STB_O相与输入到IP核的STB_I。而地址总线的最低2位被直接连接到IP核,IP核再根据这两位译码出当前操作选中的是具体哪个寄存器。

2018-08-05 08:44

在嵌入式系统领域,作为存储设备的NOR Flash和NAND Flash,大家应该不陌生。早期NOR Flash的接口是并行口的形式,也就是把数据线,地址线并排设置在I

2023-03-06 09:49

SPI一种通信接口。那么严格的来说SPI Flash是一种使用SPI通信的Flash,即,可能指NOR也可能是NAND。

2018-09-19 10:54

SPI一种通信接口。那么严格的来说SPI Flash是一种使用SPI通信的Flash,即,可能指NOR也可能是NAND。

2018-10-07 11:32

本文选用大容量NOR Flash存储器来存储配置码流,并利用JTAG接口完成配置码流下载的FPGA多配置解决方案。与System ACE方案相比,该方案不仅能快速完成多个配置码流的下载,还具有更高的配置速度和更低的实现成本。

2017-11-22 17:38

Nor Flash的接口和RAM完全相同,可以随机访问任意地址的数据,在其上进行读操作的效率非常高,但是擦除和写操作的效率很低,另外,Nor Flash的容量一般比较小,通常,Nor

2018-10-07 15:39