Xilinx的Vivado采用原理图的设计方式,比较直观适合大型项目,我们自己的code都需要封装成user IP。这里主要介绍怎么把多个关联管脚合并成类似bus的大端口。

2017-09-15 16:54

那么如何将包含XIlinx IP的用户模块封装成网表文件,下面将给出详细步骤

2023-05-18 11:12

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之

2022-04-21 08:58

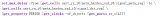

and Package,点击‘Package IP’完成对74LS00 IP的封装。6.4完成后,系统提示封装成功。4.基于Tcl的

2017-12-20 10:23

请教一下,vivado怎么把带ip核的工程进行封装,保证代码不可见,可以通过端口调用。我尝试了以下方法,ippackage,如果要在另一个程序里调用,也要提供源

2017-07-14 09:18

在给别人用自己的工程时可以封装IP,Vivado用封装IP的工具,可以得到像xilinx的

2018-06-26 11:33

在项目开发过程中,开发者出于保护核心算法的目的,希望将部分核心代码封装起来,使得其他使用者无法查看具体的代码实现细节,而不影响正常的调用。常见的思路是

2020-12-19 09:34

本文主要介绍ROM和RAM实现的verilog代码版本,可以借鉴参考下。

2023-05-16 16:57

关于仿真里的后门访问,之前的文章《三分钟教会你SpinalHDL仿真中的后门读写》中有做过介绍,其针对的都是针对以SpinalHDL中的代码进行的后门访问。今天来看看当封装了Verilog BlackBox时,在Sp

2023-07-15 10:22

Vivado提供了三种封装IP的方式:(1)将当前工程封装为IP;(2)

2021-08-10 18:09