PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等PCI SIG联合成立的Arapahoe Work Grou

2010-11-13 16:18

基于Virtex5的PCI-Express总线接口设计 PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等

2009-10-05 10:25

Virtex5无法正确读取XCF32P。 Impact可以编程到PROM和VIRTEX5,但是当Virtex5上电时,看起来PROM只在D0上输出串行数据,D1..D7为高电平(3.3V

2020-05-27 13:35

嗨,我是学生 我尝试使用virtex5与部分重新配置教程UG702,但本教程设计为virtex6(ML605)所以我需要修复它 为virtex5创建新的综合和网表(从源代码复制.v文件并运行合成

2020-06-16 07:28

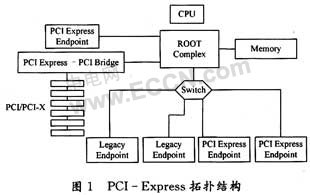

和x32的数据带宽。x1的通道能实现单向312.5 MB/s(2.5 Gb/s)的传输速率。Xilinx公司的Virtex5系列FPGA芯片内嵌PCI-ExpressEndpoint Block硬核,为实现单片可配置PCI

2020-01-19 16:52

刚刚学习FPGA,不知道怎么用virtex5,想看看例程,网上找不到,想问问各位大神,能给给看看么

2014-12-03 21:56

嗨,我正在使用virtex5,我想设置rocketIO。我红了很多文档和用户指南,但因为有太多的东西我迷路了,我不知道如何开始。感谢向导,我能够生成IP核,但是在我失去了实现IP核之后。在生成的例子

2020-06-04 11:19

“u_fifo_generator_v9_3”。引脚名称拼写错误可能导致此问题,缺少edif或ngc文件,块名称与edif或ngc文件名之间的大小写不匹配,或者类型名称的拼写错误。目标'virtex5'不支持符号'fifo_generator_v9_3'。你能帮我解决一下这个问题吗?

2020-04-26 12:14

部分可重构技术是Xilinx FPGA的一项重要开发流程。本文结合Virtex5 FPGA,详细讲解在ISE + Planahead上完成部分可重构功能的流程和技术要点。

2018-07-04 02:17

你好,我正在通过平台电缆USB使用带有iMPACT的Virtex5编程公司板。我正在使用JTAG模式,“初始化链”可以识别微处理器和FPGA并提示输入bsd / bit文件。提供这些后,我可以成功

2020-06-02 10:30