通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和配置存储器SPI FLASH为基础,从硬件电路

2014-01-24 14:17

除通过外部多功能IO来选择之外,易灵思通过内部重配置实现远程更新操作也非常简单。

2023-05-30 09:24

这里提到的局部重配置技术(Partial Reconfiguration) 是现场可编程门阵列(呵呵,就是FPGA了) 器件中的一部分。指的是在FPGA其他部分还在正常运行的情况下对其局部进行的重新配置。

2017-02-11 16:32

:不存在时延,这种方法基本不占用资源(在FPGA上占用的查找表不足300个),而且设计人员可以优化部分重配置的时序。

2017-11-22 17:08

基于Baytrail-D/I/M系列处理器开发,J1900/J1800/N2806/N2900,板载2GB/4G内存 ,

2019-10-15 17:25

的应用。在主流的FPGA中,绝大多数都采用了SRAM来存放配置数据,称为SRAM FPGA。这种FPGA的突出优点是可以进行多次配置。通过给FPGA加载不同的配置数据,即可令其实现不同的逻辑功能.FPGA这种可

2018-07-18 12:50

DCM:即 Digital Clock Manager 数字时钟管理,关于DCM的作用: 顾名思义DCM的作用就是管理,掌控时钟的专用模块。

2017-02-11 11:30

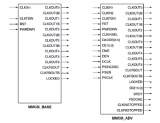

除了丰富的时钟网络以外,Xilinx还提供了强大的时钟管理功能,提供更多更灵活的时钟。Xilinx在时钟管理上不断改进,从Virtex-4的纯数字管理单元DCM,发展到Virtex-5CMT(包含

2017-02-11 09:14

有些FPGA学习者,看Xilinx的Datasheet会注意到Xilinx的FPGA没有PLL,其实DCM就是时钟管理单元。

2022-07-08 09:48

什么叫DCM(Digital Clock Management)? DCM内部是DLL(Delay Lock Loop(?)结构,对时钟偏移量的调节是通过长的延时线形成的。DCM的参数里有一个PHASESHIFT(相

2018-07-15 11:28