本文在设计实现乘法器时,采用了4-2 和5-2 混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占用率;经Xilinx ISE 和Quartus II 两种集成开发环境下的综合仿真测试,与用Verilog

2009-09-17 11:13

8乘8乘法器verilog源代码,有需要的下来看看

2016-05-23 18:21

乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。

2021-02-18 15:08

VerilogHDL语言实现的两位阵列乘法器和传统的 Booth编码乘法器进行了性能比较,得出用这种混合压缩的器乘法器要比传统的4-2压缩器构成的

2018-12-19 13:30

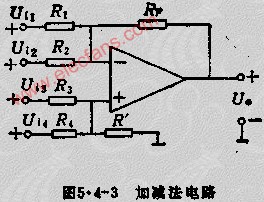

N象限变跨导乘法器 为了克服图5.4-25所示的乘法器的缺点,在基电路的基础上,采用了双重差分放大式结构,设计出如图5.4-27所示的N象限变跨导

2010-05-18 15:24

刚刚学习verilog,夏宇闻的《verilog数字系统设计教程(第三版)》中,P143中图10.3,乘法器延时为1个与门和8个全加器的延时,为什么是 8 个?我觉得应该是 10 个全加器延时,请求大神帮忙解答一下,

2014-10-10 23:04

刚接触学习FPGA,懂得verilog HDL的基础语法,有一块带XILINX的ZYNQ xc7z020的开发板,开发软件用的是vivado;现在要设计一个16位的乘法器,功能已经实现。但需要考查

2018-02-25 16:03

乘法器的基本概念 乘法器是一种完成两个互不相关的模拟信号相乘作用的电子器件。理想乘法器的输出特性方程可由下式表示: UO

2010-05-18 14:03

周期短,受到很多厂家和研究机构的关注。利用它的可编程和可扩展性,可将传统乘法器设计方法应用到FPGA芯片中。乘法器设计基本上是部分积的生成及其之间的相加的优化过程。

2019-09-03 07:16

请问关于乘法器的Verilog 程序中,移位累加具体每一步是怎么走的,自己琢磨了一番,感觉不是太懂,求高手解释。(明白二进制乘法的计算过程)

2015-10-17 23:08