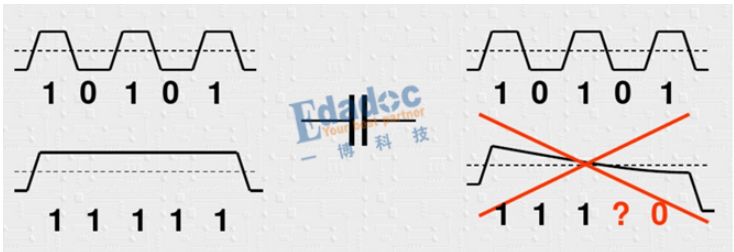

8b/10b最常见的是应用于光纤通讯和LVDS信号的。由于光模块光模块只能发送亮或者不亮,也就是0或者1这两种状态这种单极性码,那么这会存在一个问题,如果传输中出现较长的连0

2022-11-12 15:47

为了提高串行数据传输的可靠性,现在很多更高速率的数字接口采用的是对数据进行编码后再做并串转换的方式…

2018-03-14 16:23

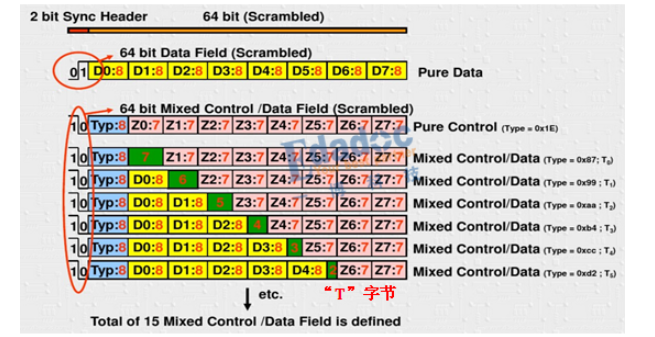

很多人可能在想,8B/10B编码主要作用的优化直流平衡,从8bit中插2个bit进去,这样的话最终效果能够使长0或者长1的位数不超过5位,达到很好的效果。那64

2021-04-01 12:01

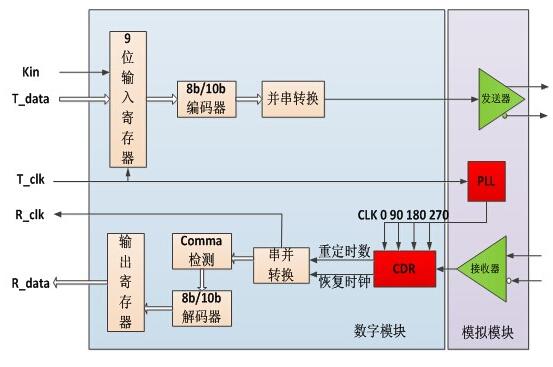

下面详细介绍了6个功能模块及其应用特点:并行接口、串行接口、时钟分布电路、8B/10B编解码电路、PRBS测试以及相关寄存器访问控制接口MDIO。

2021-06-26 16:10

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格

2015-02-02 17:32

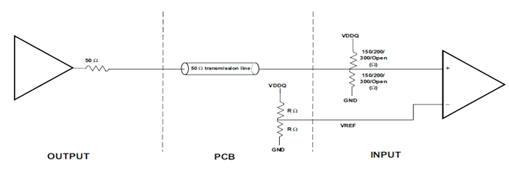

在高速链路中导致接收端眼图闭合的原因,很大部分并不是由于高频的损耗太大了,而是由于高低频的损耗差异过大,导致码间干扰严重,因此不能张开眼睛。针对这种情况,前面有讲过可以通过CTLE和FFE(包括DFE)均衡进行解决,原理无非就是衰减低频幅度或者抬高高频幅度,从而达到在接收端高低频均衡的效果。 隔了一段时间,不知道大家还记得我们这个约定吗?不管你们记不记得,本人肯定没有忘记哈。现在就把这个关子拿出来讲讲,也就是今天

2021-04-01 12:04

需要注意的是PCIe Spec并没有规定弹性缓存的具体位置,设计者可以将弹性缓存放在8b/10b解码器之前,也可以把弹性缓存放在8b/

2018-09-08 09:59

XSTC_8B10B IP(XSTC:XiST Transmission Channel)是智多晶开发的一个灵活的,轻量级的高速串行通信的IP。IP在具备SerDes(单通道或多通道)高速串行收发器之间构建出接口简单,低成本,轻量化的高速率数据通信通道。

2025-04-03 16:30

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的 10 位8b/10b 编码,并串转换用于将

2019-05-27 14:31

串行互连接口的速率在过去几年里得到了显著提高,每线的速率从2.5Gbit/s提高到10Gbit/s,而每个接口可以容纳1到32线。8B10B作为互连接口的一种编码技术,设计简单、性能出众,因此成为

2020-04-12 11:06