电子发烧友网站提供《基于PCIE总线的多DSP系统接口设计和

2023-10-24 09:36

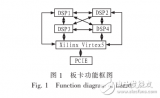

本文开发了多DSP雷达信号处理板卡。对DSP互连、DSP与FPGA通信以及基于Xilinx FPGA的

2012-05-29 17:15

PCIE总线的多DSP系统接口设计

2017-10-31 10:42

开发了多DSP雷达信号处理板卡。对DSP互连、DSP与FPGA通信以及基于Xilinx FPGA的

2012-05-28 17:40

未能够检测到设备,请各位大神指教:1、此DSP6678的PCIe能否直接连接机箱PCIe卡槽的方案是否可行?2、若方案可行,是否需要手动开发底层

2018-08-02 07:16

时钟驱动模块产生,可以作为整个系统的时间基准。另外3条信号线由l号槽的电源监控模块产生。3 系统接口设计方案通常,设计多

2019-04-22 07:00

在同一个Bank内打开两页。 2.4 DSP/SDRAM接口性能 33MHz、32位的PCI总线理论极限速度是132MB/s,实际速度要有一些折扣。由于FPGA访问DSP

2019-05-17 07:00

本文首先介绍了多DSP共享总线的通用信号处理板卡的硬件结构,介绍了基于PCI9054的CPCI总线接口设计和FPGA控制

2011-09-09 11:51

通用多DSP目标系统由那几部分构成?基于ISA总线的通用多DSP目标

2021-04-13 06:06

摘要:介绍了PCI总线控制芯片PCI2040的功能及内部结构,分析了基于PCI总线的双DSP通信的硬件结构及实现方法,并描述了利用Windows2000 DDK开发WD

2019-09-24 22:18