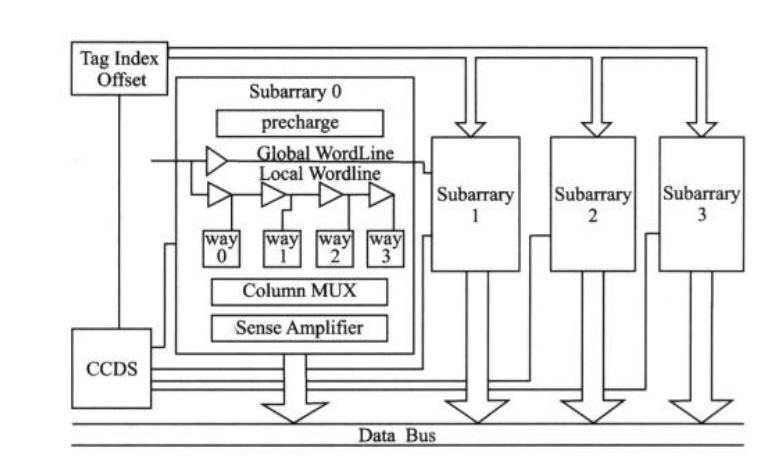

当下,最火的学问莫过于“大数据”,大数据的核心思想就是通过科学统计,实现对于社会、企业、个人的看似无规律可循的行为进行更深入和直观的了解。FPGA的可测性也可以对FPGA内部“小数据”的统计查询,来实现对

2014-07-28 11:56

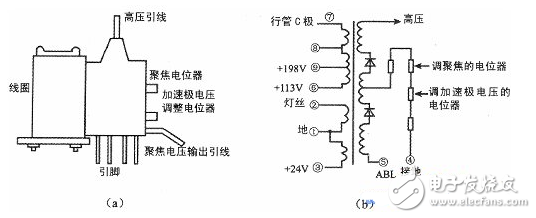

行逆程的电容大小,也决定高压的大小,在逆程电容容量小时,就会使行管导通次数变快,使行输出变压器输出电压增高,也会使图像的行

2017-06-01 09:00

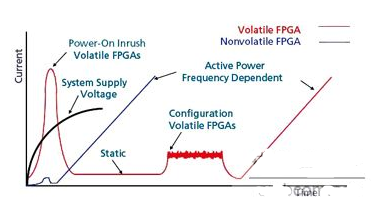

随着便携和以电池供电的应用快速增加,低功耗设计已成为延长电池寿命所不可或缺的任务。此外,在决定产品尺寸、重量、和效率时,功耗也扮演了重要角色。由于消费性电子的生命周期越来越短,具可程序特性,且能轻松

2020-07-20 17:53

(Field Programming Gate Array, FPGA)。可重构系统非常适合于那些对功耗有严格要求或者计算密集的应用,因为此类应用在FPGA上实现的功耗要大大低于在处理器上实现的功耗

2018-07-11 11:20

随着异步编程的发展以及各种并发框架的普及,协程作为一种异步编程规范在各类语言中地位逐步提高。我们不单单会在自己的程序中使用协程,各类框架如fastapi,aiohttp等也都是基于异步以及协程进行实现。那到底什么是协

2024-01-26 11:36

部分可重构技术是Xilinx FPGA的一项重要开发流程。本文结合Virtex5 FPGA,详细讲解在ISE + Planahead上完成部分可重构功能的流程和技术要点

2018-07-04 02:17

goroutine 是轻量级线程,调度由 Go 运行时进行管理的。Go 语言的并发控制主要使用关键字 go 开启协程 goroutine。Go 协程(Goroutine)之间通过信道(channel)进行通信,简单的说就是多个协程之间通信的管道。信道可以防止多个协

2022-09-19 15:06

基于SRAM的FPGA的问世标志着现代可重构技术的开端,并极大地推动了其发展。可编程FPGA可以根据不同算法设计合理的硬件结构,以达到提高执行效率的目的。动态可重构

2017-11-25 10:20

本文主要介绍了行输出变压器工作原理_行输出变压器动态检测仪以及故障判断方法。行输出变压器简称FBT,又称为行回扫变压器或行

2018-03-12 11:14

宽程电子定时器电路

2008-08-11 08:25