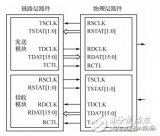

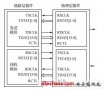

SPI4.2总线是一种芯片间的互连总线,连接芯片的链路层和物理层模块。其工作时钟是源同步双边沿触发时钟,至少为311 MHz。图1是使用SPI4.2总线连接两个芯片的示意图。可见,SPI4.2总线

2018-07-12 13:37

SPI4.2总线(System Packet Interface,系统间数据包接口)是一种速度高达10 Gb/s的芯片间互连总线,主要应用于ATM信元传输、POS(Packet Over SONET/SDH,基于SONET/SDH的包传输)和10 Gb/s以太网等

2012-01-04 15:56

SPI-4.2(System Packet Interface)是 OIF(Optical Internetworking Forum)定义的局部高速总线标准,用于 PHY层芯片到链路层芯片

2020-08-18 16:51

SPI-4.2(System Packet Interface)是 OIF(Optical Internetworking Forum)定义的局部高速总线标准,用于 PHY层芯片到链路层芯片

2020-11-25 17:19

市場研究調查認定的 一項突破性數位設計分析技術 Tektronix 已經開始一項創新的機種,以新的概念及生產系列以

2010-08-06 08:30

利用源同步接口,数据的有效窗口可以提高很多。通常频率都在1GHz以下。在实际应用中可以见到如SPI4.2接口的时钟可以高达DDR 700MHz x 16bits位宽。DDR Memory

2023-03-28 15:51

串行外围接口 大致了解: spi是个同步协议,数据在master和slaver间交换通过时钟sck,由于它是同步协议,时钟速率就可以各种变换。 sck:主机提供,从机不能操控,从器件由主机产生的时钟控制。数据只有在sck来了的上升沿或者下降沿才传输。 高级一点的

2024-11-16 10:35

一、SMT-PCB上元器件的布局 1、当电路板放到回流焊接炉的传送带上

2006-04-16 21:43

、闪存芯片等设备与MCU之间通讯。SH32F9001包含2个独立的串行外设接口SPI0/1,主从机可选,10个可编程主时钟频率,极性相位可编程,数字位宽8/16位可选,支持DMA通信,带MCU中断的主模式故障出错标志

2024-12-31 17:04

SPI 总线是一个同步串行接口的数据总线,具有全双工、信号线少、协议简单、传输速度快等特点。介绍了SPI 总线的结构和工作原理,对4 种工作模式的异同进行了比较,并着重分析了

2012-05-23 10:18