本文主要讲解的是FPGA高速收发器的来源,着重从三个方面解析,可能部分理解会存在有错误,想要不一致的可以来评论区交流哦。

2024-07-18 11:13

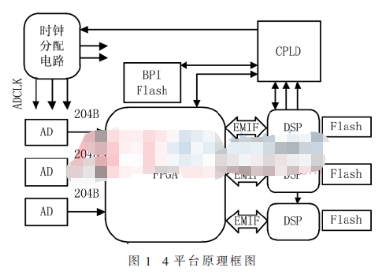

DSP与FPGA高速的数据传输有三种常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 现场可编程逻辑门阵列) 设计 FIFO的接口电路,即可实现

2017-02-11 14:16

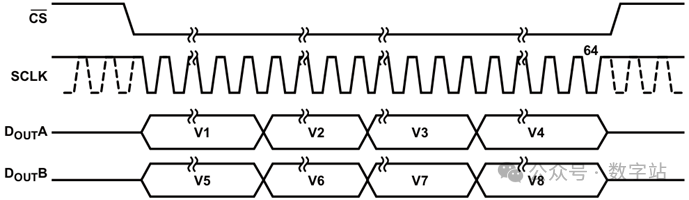

与赛灵思FPGA连接的数据转换器正迅速采用全新JESD204B高速串行链路。要使用该接口格式及协议,设计必须考虑一些基本硬件及时序问题。

2018-07-19 13:51

随着现场可编程门阵列(FPGA)已发展成为真正的可编程系统级芯片,利用这些芯片设计印制电路板(PCB)的任务变得愈加复杂。要完全实现FPGA的功能,需要对PCB板进行精心设计。采用高速

2017-11-23 14:18

数据采集系统的总体架构如图1所示,其中PCI核、DMA控制器与A/D控制器均在FPGA内部实现。为实现多路并行采样,可选用多片A/D器件并行处理的方式,在FPGA的高速

2018-08-28 10:16

高速串行通信的“高速”一般比较高,基本至少都会上G。如果利用FPGA内部的LUT、触发器和普通IO是无法满足这样高的输入输出速率的。

2024-08-05 11:12

新型多通道通用信号处理平台主要包括高速AD芯片、Xilinx最新UltraScale系列FPGA和TI的多核DSP,原理框图如图1所示。其中FPGA和

2020-07-16 09:25

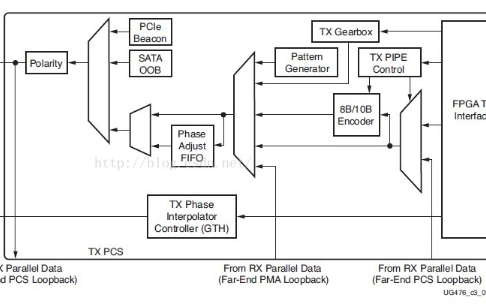

随着FPGA应用范围的不断扩大以及对速度需求的不断提升,集成高速串行模块的FPGA已经应用于市场。以Xilinx的Virtex5系列为代表的集成GTPRocketIO模块的F

2018-07-20 11:42

FPGA内部并行数据通过FPGATX Interface进入TX发送端,然后经过PCS和PMA子层的各个功能电路处理之后,最终从TX驱动器中以高速串行数据输出。

2020-03-29 17:09

。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有,最后具体介绍),根本不担心使用。

2018-06-30 10:23