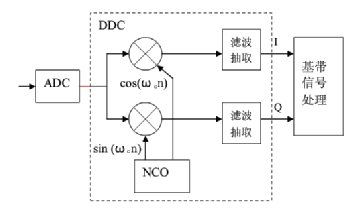

积分梳状滤波器(CIC,Cascaded Integrator Comb),一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC 滤波器结构简单,没有乘法器,

2023-03-27 11:40

在实现多级CIC滤波器前我们先来了解滑动平均滤波器、微分器、积分器以及梳

2019-06-22 10:35

加法器、积分器和寄存器,适合于工作在高采样率条件下,而且CIC滤波器是一种基于零点相消的FIR

2023-04-12 10:26

ISE 12.3在Xilinx xc5vsx95t-2ff1136 FPGA上实现了一种下采样率为64的抽取滤波器。Modelsim仿真结果表明,该抽取滤波器设计是有

2017-11-17 09:01

滤波器(降2倍)组成。为了实现高频工作,CIC滤波器采用两级结构,第一级采用多相分解技术,使大部分结构工作在较低时钟频率下,极大地降低了

2018-02-21 12:08

在数字信号处理系统中,有限脉冲响应(finite impulse response,FIR)数字滤波器是一个非常重要的基本单元。近年来,由于FPGA具有高速度、高集成度和高可靠性的特点而得到快速发展

2024-11-05 16:26

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,

2018-04-28 11:50

这个概念是相对于单速率(Single Rate)信号处理而言的。单速率 是指整个信号处理流程中只有一种数据速率;多速率 是指系统中存在多个数据速率。使用多速率信号处理可以节省存储空间、减少通信数据量、减少运算量、减轻设计难度。

2024-12-30 15:10

本文简要介绍了FIR数字滤波器的结构特点和基本原理,提出基于FPGA和DSP Builder的FIR数字滤波器的基本设计流程和实现方案。##FIR 数字

2014-07-24 15:30

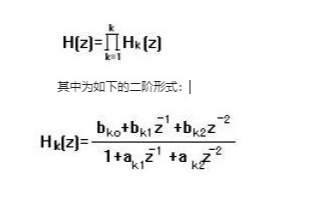

IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同时钟速度下可以提供

2020-03-04 10:32