乘法器(multiplier)是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算

2021-02-18 15:08

本文在设计实现乘法器时,采用了4-2和5-2混合压缩器对部分积进行压缩,减少了乘法器的延时和资源占 用率;经XilinxISE和QuartusII两种集成开发环境下的综合仿真测试,与用

2018-12-19 13:30

在数字信号处理中,乘法器是整个硬件电路时序的关键路径。速度和面积的优化是乘法器设计过程的两个主要考虑因素。由于现代可编程逻辑芯片FPGA的集成度越来越高,及其相对于AS

2019-09-03 07:16

本设计以16位乘法器的设计为基础,从而掌握现代大规模集成数字逻辑电路的应用设计方法,进一步掌握电子仪器的正确使用方法,以及掌握利用计算机进行电子设计自动化(EDA)的基本方法。由16位加法器构成的以

2021-06-01 09:43

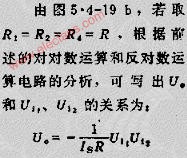

乘法器对数运算电路应用 由对数电路实现乘法运算的数学原理是:UO=EXP(INU11+INU12)=U11+U12

2010-04-24 16:03

本文着重介绍了一种基于WALLACETREE优化算法的改进型乘法器架构。根据FPGA内部标准独特slice单元,有必要对WALLACE TREE部分单元加以研究优化,从而让在FPGA的

2011-11-17 10:50

乘法器的基本概念 乘法器是一种完成两个互不相关的模拟信号相乘作用的电子器件。理想乘法器的输出特性方程可由下式表示: UO

2010-05-18 14:03

模拟乘法器作用及电路

2017-10-23 09:22

刚接触学习FPGA,懂得verilog HDL的基础语法,有一块带XILINX的ZYNQ xc7z020的开发板,开发软件用的是vivado;现在要设计一个16位的乘法器,功能已经实现。但需要考查

2018-02-25 16:03

乘法器在通信电路中的应用 普通振幅调制

2010-05-18 17:46