60Hz,逐行扫描时为30帧/s。其像面大小为1/3英寸,支持8位或16位数字信号从单通道或双通道输出,输出信号的类型可在YCrCb和RGB 之间选择,图像矩阵支持VGA或CIF 规定, 数字输出

2020-04-04 11:11

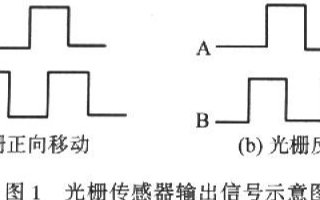

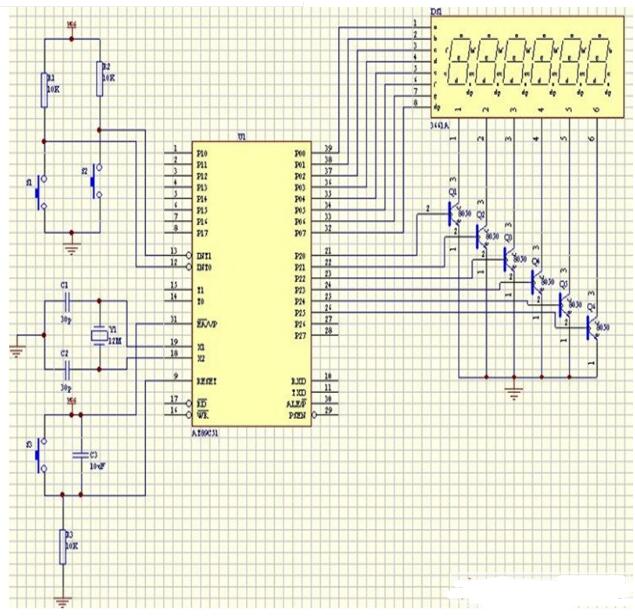

作者:金锋 , 卢杨 ,王 文松 , 张玉平 给出一种新的光栅位移传感器的四倍频细分电路设计方法。采用可编程逻辑器件(CPLD)设计了一种全新的细分模块,利用Verilog HDL语言编写四倍频细分、辨向及计数模块程序,并进行了仿真。仿真结果表明,与传统方法相比,新型的设计方法开发周期短,集成度高,模块化,且修改简单容易. 光栅位移传感器是基于莫尔条纹测量的一种传感器,要提高其测量分辨率,对光栅输出信号进行细分处理是必要环节.在

2021-03-28 11:33

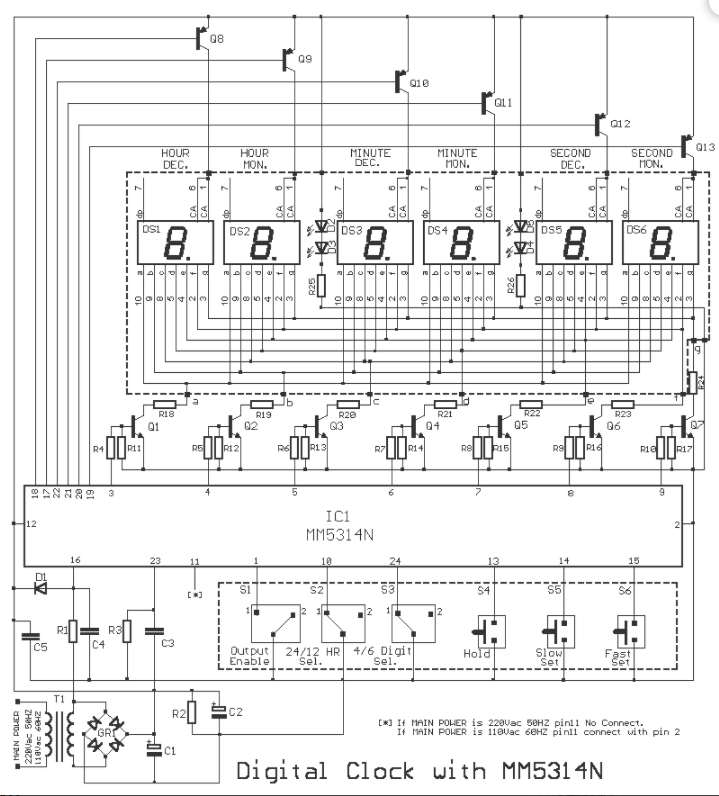

本文主要介绍了七款数字时钟设计电路图。数字钟是一种用数字电路技术实现时、分、秒计时的钟表。与机械钟相比具有更高的准确性和

2018-01-26 11:14

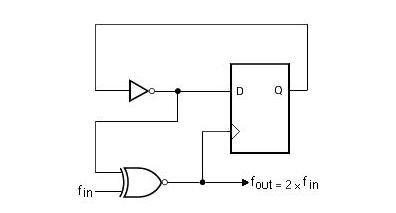

一个数字倍频电路 这个就是原理图,奉上代码 1

2020-11-09 14:53

这是基于IC MM5314N的数字时钟电路图。时钟显示使用 6 个 7 段 LED,格式为 HH:MM:SS。该电路的电源已包含在内,因此您可以将该电路直接连接到电源。

2022-06-21 16:41

首先肯定是在本时钟域内的clk_en会先变低(invalid),之后才会使得另外时钟域内的clk_en变高(valid),这时另外一个时钟域内的时钟才能和clk_en相

2020-11-10 15:06

了解时钟信号的数字定时以及诸如抖动、漂移、上升时间、下降时间、稳定时间、迟滞和眼图等常用术语。本教程是仪器基础教程系列的一部分。发送数字信号其实发送的就是一串由0或1组

2017-11-17 08:36

数字设计中的时钟与约束 本文作者 IClearner 在此特别鸣谢 最近做完了synopsys的DC workshop,涉及到时钟的建模/约束,这里就来聊聊数字中的

2023-01-28 07:53

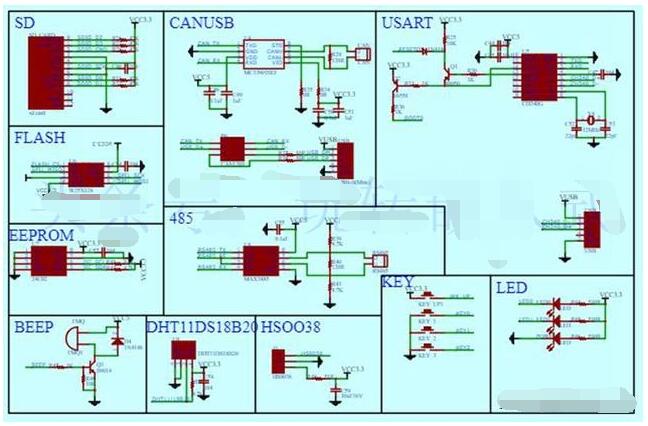

从事产品研发是需要设计硬件电路原理图的,同时也要看别人的电路原理图,对于一个功能比较多的产品,电路图的内容是非常多的,如何才能高效的看懂别人的原理图呢?

2020-06-25 17:55

特殊时钟电路图

2009-07-16 11:01