前置放大器電路,雖然電路結構非常簡單,但是想要用到1200MHz時,就要注意到引線電感量( Lead Inductance)的影響,所以配線要儘量短。電路例係利用Glass Epoxy 雙面基板組成寬

2018-09-20 18:45

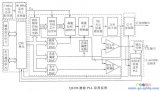

摘 要:结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨

2012-06-25 13:53

pll频率合成器工作原理与pll频率合成器的原理图解释 我们要搞清楚pll频率合

2023-02-24 18:19

已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性

2022-10-14 10:30

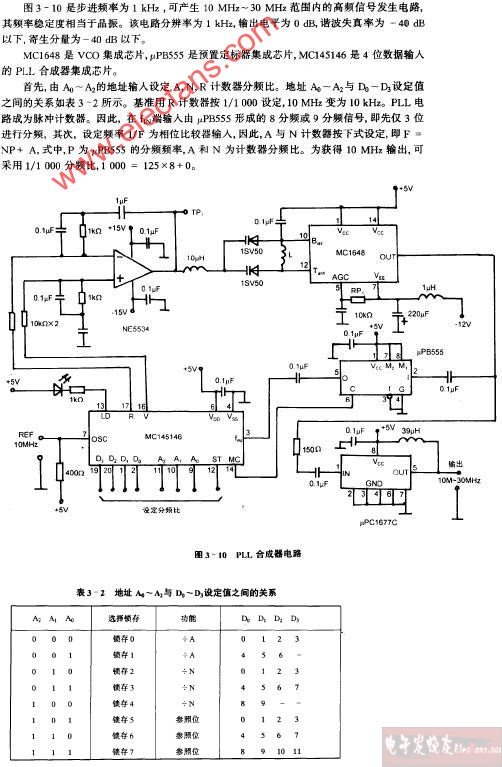

PLL合成器电路图

2009-07-14 17:08

DDS+PLL高性能频率合成器的设计方案 频率合成理论自20世纪30年代提出以来,已取得了迅速的发展,逐渐形成了直接频率合成技术、锁相频率

2010-04-17 15:22

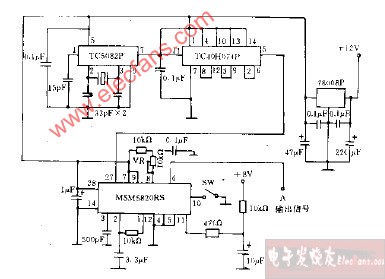

采用PLL的频率合成器电路图

2009-07-20 11:38

ADI推出的 ADF4158 PLL 合成器 ADI最新推出的 ADF4158 PLL 合成器,可灵活 、高性价比地实现 FMCW (频率调制连续波)雷达系统。FMC

2010-01-13 11:38

下图所示的是用 Q2230 激励锁相倍频系统实现的一个实际的 频率合成器 。系统时钟采用40 MHz,这样能输出DC~15 MHz、分辨率为0.01 Hz、电压峰一峰值为10 V的正弦波。谱纯度优于

2018-03-17 11:13

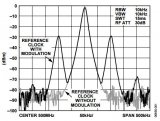

直接数据频率合成器(DDS)因能产生频率捷变且残留相位噪声性能卓越而著称。另外,多数用户都很清楚DDS输出频谱中存在的杂散噪声,比如相位截断杂散以及与相位-幅度转换过程相关的杂散等。此类杂散是实际

2019-11-14 17:10