本设计已实用于国家863计划“可扩展到T比特的高性能IPv4/v6路由器基础平台及实验系统”项目中。其主要功能是对主控部分的FPGA读取Flash进行控制。

2020-07-15 17:47

首先抛出重点:使用Xilinx的平台,最大的难点在于,要自己设计一个Flash读写控制器。

2023-08-03 09:34

CPLD内部施密特触发器电器特性见表1。目前大部分使用的CPLD都需要两个电源VCC和VCCIO,VCC就是CPLD内部的核电压,VCCIO是CPLD所有I/O 引脚电

2018-05-11 08:22

数字系统的设计人员擅长在其印制电路板上用FPGA和CPLD将各种处理器、存储器和标准的功能元件粘合在一起来实现数字设计。除了这些数字功能之外,FPGA和CPLD还可以使用LVDS输入、简单的电阻电容(RC)电路和一些

2018-04-26 11:53

的通用性;此外CPLD内部有丰富的逻辑资源,可将用户控制逻辑和PCI接口逻辑在同一块芯片中实现,这样不仅充分利用了逻辑资源,还能使系统设计显得更加紧凑。

2020-03-20 09:54

费时费力且还需拆结构。若在FPGA内部通过逻辑代码搭建一Flash控制器实现对Flash器件的读写操作,即可并行实现系统

2020-01-27 16:17

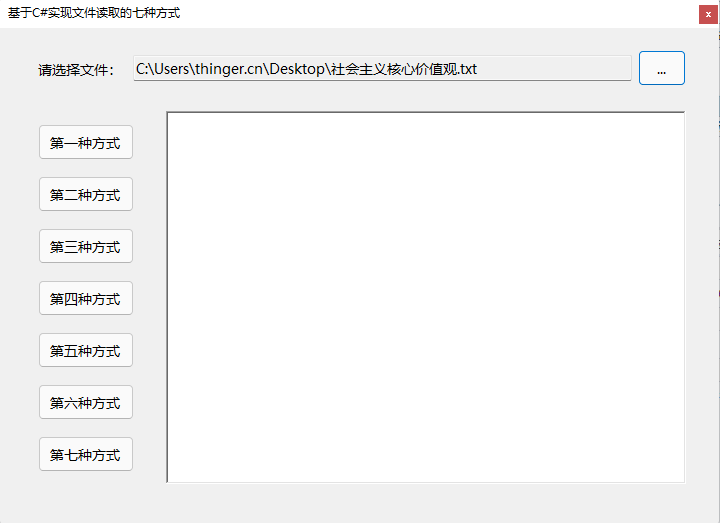

文本读取在上位机开发中经常会使用到,实现的方式也有很多种,今天跟大家分享一下C#实现读取读取的7种方式。基于FileSt

2023-02-22 15:38

CPLD通常用于实现前面提到的简单组合逻辑功能,并负责“引导”FPGA以及控制整个电路板的复位和引导顺序。

2018-09-27 11:56

[1] 。它比起传统的并行总线接口Flash 来说节省了很多的I/ O 口资源,从而为系统功能的扩展提供了更多的可能。为此提出了一种基于FPGA 的SPI Flash 控制器的设计方法,并用

2017-11-22 08:47

Flash读写硬件实现方案,该方案利用硬件对SPI Flash进行控制,能够非常方便地完成Flash的读写、擦除、刷新

2013-09-24 09:12