两个频率相同的交流电相位的差叫做相位差,或者叫做相差。 这两个频率相同的交流电,可以是两个交流电流,可以是两个交流电压,可以是两个交流电动势,也可以是这三种量中的任何两个。两个同频率正弦

2017-08-21 00:34

CPLD内部施密特触发器电器特性见表1。目前大部分使用的CPLD都需要两个电源VCC和VCCIO,VCC就是CPLD内部的核电压,VCCIO是CPLD所有I/O 引脚电

2018-05-11 08:22

STM32 通过 FSMC 读写CPLD 的程序,CPLD挂在STM32的地址线和数据线上,将CPLD看做片外RAM的方式来进行读写,在我做的板子上CPLD挂在第四个区

2018-04-20 10:38

都是FPGA/CPLD逻辑设计的内在规律的体现,合理地采用这些设计思想能在FPGA/CPLD设计工作种取得事半功倍的效果。

2023-05-18 08:56

FPGA LAB和CPLD的LAB设计不同。CPLD LAB由宏单元构成,包括自己的本地可编程阵列,而FPGA LAB由大量的逻辑模块构成,这些模块被称为逻辑单元,即LE,而且本地互连和逻辑分开。LE看起来可能和CPLD

2018-04-17 17:02

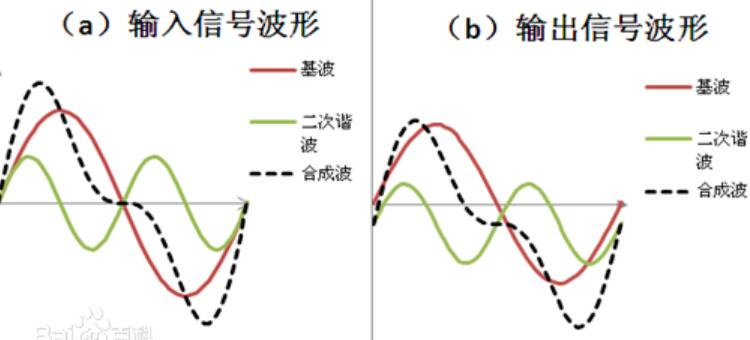

相位失真是指信号由放大器输入端至输出端所产生的时间差(相位差)导致的失真,不同频率的信号经过处理器后,由于时延各不相同,从而导致相位失真。这个时间差自然是越小越好,否则会影响负回输线路的工作。除此之外

2019-09-26 09:41

AMD公司最先生产带有宏单元的可编程逻辑器件PAL22V10。目前PAL22V10已成为划分PLD的界限。可编程逻辑器件所包含的门数大于PAL22V10所包含则门数,就被认为是复杂可编程逻辑器件,即CPLD。

2018-05-24 01:39

当电路频率相同时,相量是分析交流电路中元件行为的有效方法。 两个向量相加的结果取决于它们的相对相位,它们是“同相”还是“异相”,因为存在一些相位差。

2023-03-01 17:33

CPLD和FPGA都是由逻辑阵列模块构成的,但是CPLD的LAB基于乘积和宏单元,而FPGA的LAB使用基于LUT的逻辑单元。CPLD的LAB围绕中心全局互连排列,随着器件中逻辑数量的增加,呈指数

2024-01-23 09:17

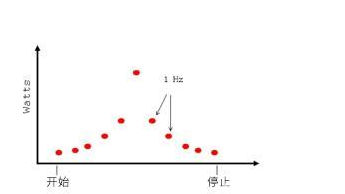

在许多高端通信应用中都会使用到晶振,为了更好地保证设备高效使用,消除相位噪声来保持电子RF电路中强大的频率稳定性非常重要。对于雷达系统中的精确瞄准和其他通信系统中的频谱纯度而言,尤其如此。让我们深入研究一下晶振相位噪声和抖动的含义。这将帮助您更好地了解为什么降低系

2021-03-27 11:27