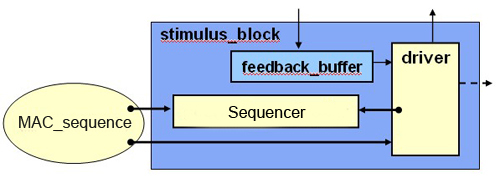

在系统芯片的设计中,传统的激励发生机制耗费人工多且难以重用,严重影响了仿真验证的效率。针对此问题,构建了一种基于可

2017-11-28 17:43

本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试

2023-06-13 09:14

采用System Verilog语言设计了一种具有层次化结构的可重用验证平台,该平台能够产生各种随机、定向、错误测试向量

2018-01-12 11:28

本文介绍了从一组可重用的验证组件中构建测试平台所需的步骤。UVM促进了重用,加速了测试

2023-06-13 09:11

本文介绍了一种使用软件作为激励以加速系统级验证的方法。使用的激励是切合实际的,并易于快速创建。对设计执行此激励可及早揭露

2013-01-04 14:51

先进的设计与仿真验证方法成为SoC设计成功的关键。一个简单可行的SoC验证平台,可以加快

2019-10-11 07:07

设计了一种基于FPGA的验证平台及有效的SoC验证方法,介绍了此FPGA验证软硬件

2017-11-17 03:06

SoC基于IP设计的特点使验证项目中多语言VIP(Verification IP)协同验证的需求不断增加,给验证工作带来了很大的挑战。为了解决多语言VIP在

2015-12-31 09:25

Open Verification Methodology(OVM)是Mentor Graphics 和Cadence 共同推出的,业界第一个基于SystemVerilog、通用开放的验证方法学;其基于事务交易级的方法学,基于Factory Pattern 的对象生

2010-07-04 11:43

随着深亚微米工艺技术日益成熟,基于IP复用的IC设计方法广泛采用,集成电路芯片的规模越来越大,这对集成电路验证技术和方法学提出了很大的挑战。就如芯片

2009-04-04 10:58