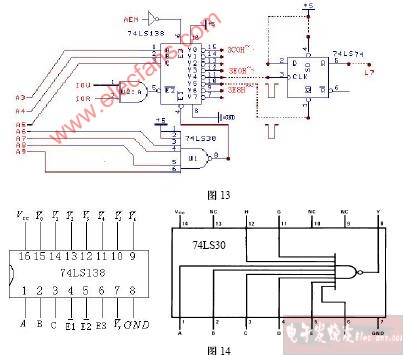

实验一 I/O地址译码一)实验目的掌握I/O地址译码电路的工作原理。二)实验内容1. 实验电路如图13所示,其中74LS74为D触发器,可直接使用实验台上数字

2009-03-25 10:57

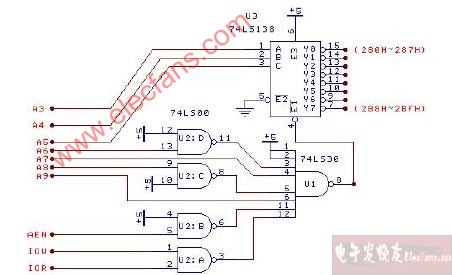

IO接口地址译码电路 如上图1所示地址空间280H~2BFH共分8条译码输出线:Y0~Y7 其地址分别是280H~28

2009-03-25 09:27

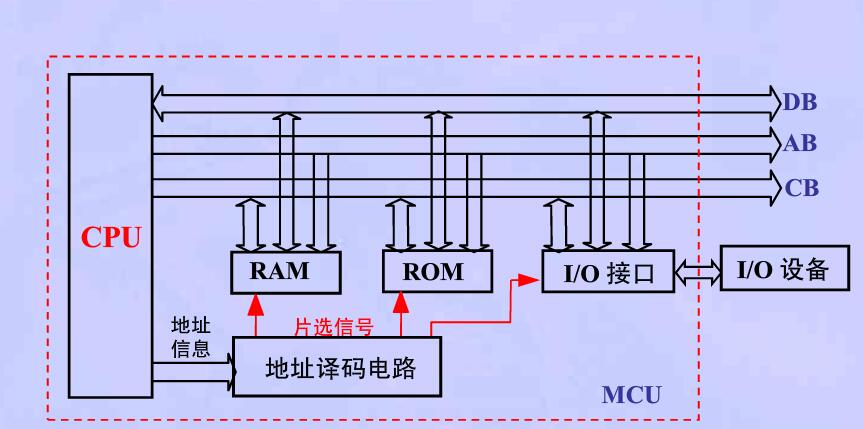

地址译码有两种方式,一种是单译码方式,或称为字结构方式;另一种是双译码方式,或称为X-Y译码结构。

2018-03-02 16:11

Wishbone部分地址译码的实现如图26所示。对于图中所示IP核,我们假设其只有4个地址,对应4组寄存器。地址译码器首

2018-08-05 08:44

方式。常用的为独立编制形式,即外设端口地址不同内存地址一起统一编址。并配有专门的I/O指令:IN/OUT(不同于内存的mov指令)。端口地址译码即根据

2017-11-16 09:40

译码和显示译码两类。译码器的分类:二进制译码器,二-十进制译码器,显示译码

2018-04-04 11:51

常用的译码电路有哪些?本文主要介绍了IO接口地址译码电路、BCD译码驱动器电路、4线16线译码电路、3.8线

2018-03-02 15:48

提出了一种使用CPLD解决双端口RAM地址译码和PCI接口芯片局部总线仲裁的的硬件设计方案,并给出了PCI总线接口芯片

2011-01-07 12:13

CH341与BUS并口方式应用 图中通过74LS373 进行地址锁存,比MEM并口方式能够提供更多的地址线,如果外加地址译码

2010-01-06 17:43

总线使用单端并行数据总线,采用地址译码方式进行数据传递,而采用ID译码方式进行配置信息(比如配置某个PCI设备的物理地址)的传递。其中

2023-01-30 15:34