先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入

2020-03-29 17:19

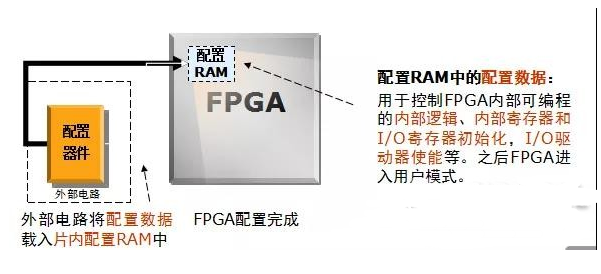

每次在系统掉电之后,之前载入的程序将会丢失,系统上电后需要重新配置。设计者为了弥补这项缺陷,在

2024-10-24 18:13

通过FPGA的多重配置可以有效地精简控制结构的设计,同时可以用逻辑资源较少的FPGA器件实现需要很大资源才能实现的程序。以Virtex5系列开发板和

2014-01-24 14:17

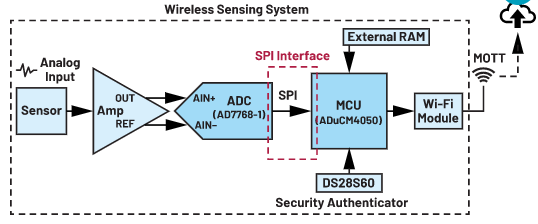

ADC和DAC是FPGA与外部信号的接口,从数据接口类型的角度划分,有低速的串行接口和高速的并行接口。FPGA经常用来采集中高频信号,因此使用并行

2022-04-21 08:55

感谢发烧友/* attach spi device */static int rt_spi_device_init(void){ struct rt_spi_configuration cfg

2024-06-04 09:21

广义的来说,FPGA的配置包括直接使用下载电缆对FPGA器件进行编程、对外部EEPROM和FLASH进行编程、使用MPU对FPG

2016-10-26 10:58

下面我们来看本实例如何配置一个PLL硬核IP,并将其集成到工程中。如图8.18所示,在新建的工程中,点击菜单“ToolsàMegaWizard Plug-In Manager”。

2018-04-24 11:30

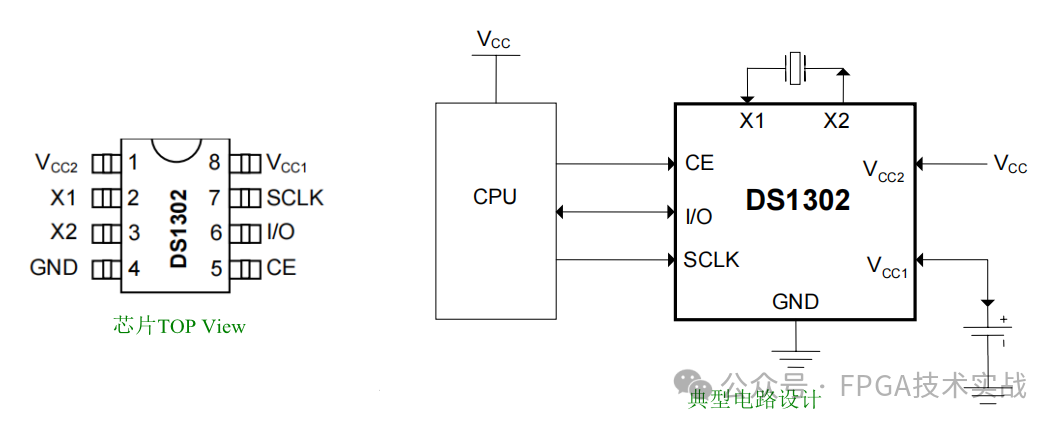

本文通过以DS1302芯片为基础,介绍该芯片与FPGA之间SPI通信原理,详细描述硬件设计原理及FPGA

2024-10-24 14:16

。此外本文提出,激活DMA控制器释放内核也可以加快连续数据事务处理的流程。在DMA的乒乓模式下,DMA的配置时间可通过适当的调度来节省。在此基础上,还可以通过直接指定中断引脚的方式优化中断处理函数。

2023-06-12 15:26

常见的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),还有通用的串行 SPI FLASH

2020-04-06 10:33