当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

随着近些年我国经济的快速发展,我国也是出现了许多的巨头企业,这些巨头企业不仅实力相当的雄厚,市值也是非常的可观,那么目前国内市值最高的公司又有哪些呢?无独有偶,近日胡润发布的“中国市值最大的公司”数据也是告诉了我们答

2019-10-20 10:33

信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出

2017-12-13 16:26

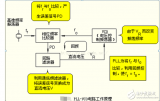

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

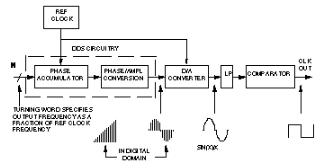

新的集成完整DDS产品为敏捷频率合成应用提供了一种有吸引力的模拟PLL替代方案。长期以来,直接数字频率合成 (DDS) 一直被认为是生成高精度、频率捷变(宽范围内可快速变化的频率)、低失真输出波形的卓越技术。

2023-01-30 09:51

的Tick数就是基于模块时钟的)。本系列文章就来详细介绍TC3xx芯片的时钟系统及其具体配置。本文为TC3xx芯片时钟系统的锁相环PLL详解。

2023-12-01 09:37

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短

2018-05-11 15:14

近几年,国内PCB企业频频发力,取得瞩目成绩。更有不少企业成功往资本市场靠岸,借助资本力量强大自身。

2019-04-25 14:16

本文分析了国内外 AI 芯片的格局和特点,作者认为,在AI芯片领域,国外芯片巨头占据了绝大部分市场份额,不论是在人才聚集还是公司

2018-04-05 14:28