一般情况下,FPGA器件内部的逻辑会在每个时钟周期的上升沿执行一次数据的输入和输出处理,而在两个时钟上升沿的空闲时间里,则可以用于执行各种各样复杂的处理。而一个比较耗时的复杂运算过程,往往无法一个

2018-05-23 05:56

为了正确理解时钟相关器件的抖动指标规格,同时选择抖动性能适合系统应用的时钟解决方案,本文详细介绍了如何理解两种类型时钟驱动器的抖动参数,以及从锁相环输出噪声特性理解时钟

2013-06-21 15:40

对于数据处理速率与准确度需求较高,且功能较多、信息交互复杂的应用场景,往往需要时钟芯片的存在,如通讯基站、交换机、数据中心服务器、汽车、工业控制等。今天给大家推荐一款国产时钟芯片,可完全替代TI的LMK04828。

2024-09-14 15:03

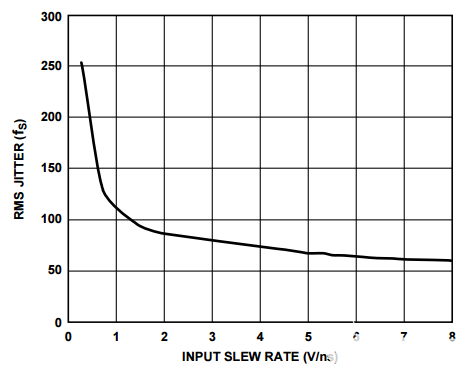

PCB走线的行为类似于低通滤波器,当时钟信号沿走线行进时会衰减,并随着走线长度的增加而增加脉冲边沿失真。较高频率的时钟信号会受到更大的衰减、失真和噪声的影响,但为了改善抖动(在低压摆率下最差)(图

2023-01-30 11:48

内建晶体单元的实时时钟模块的特征【序文】社会中存在着为数众多的需要更精确时间的应用程序,例如金融处理系统、安全系统、电表、产业用测试仪器、办公自动化工具、医疗或娱乐产品等。为了获得精确的时间,必须

2024-08-16 14:00 Piezoman压电侠 企业号

饥渴型社会的更高期望。随着这些标准新版本的推出,市场对支持它们的电子电路的需求也加强了。集成在当代系统应用中的高性能时钟产生及分配器件使用频域参数,也就是相位噪声和相位抖动来描述它们的性能。本文探讨相位

2021-06-28 15:52

时钟合成器和时钟发生器是两种用于产生时钟信号的电子器件,它们在功能和应用上有一些区别。

2023-11-09 10:26

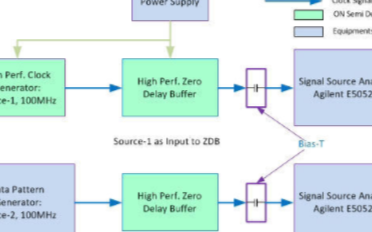

在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动,然后同时再生出低相位抖动的跟随时钟

2017-11-18 12:08

北斗系统,作为一个庞大的卫星星座,每一颗卫星都是由几万个元器件组成的,其核心元器件国产化率达到了100%。其中,行波管放大器作为卫星上用来放大信号的关键部件,是多年来的“卡脖子”技术。

2020-10-09 11:25

时钟树综合,通常我们也叫做CTS。时钟树综合就是建立一个时钟网络,使时钟信号能够传递到各个时序器件。CTS是布局之后相当

2022-09-05 10:11