在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每

2020-11-22 11:54

数字电路中,每个操作都需要在正确的时间执行,因为电子元件并不是瞬间完成其功能的。例如,在时钟信号的上升沿或下降沿处将数据写入存储器,然后等待一段时间后读取数据。如果在错误的时序下执行这些操作,从机数据接收错误,导致乱码,(奇偶校验位就是防止数据乱码)

2023-11-03 16:27

传输线的定义是有信号回流的信号线(由两条一定长度导线组成,一条是信号传播路径,另一条是信号返回路径),最常见的传输

2020-11-06 10:25

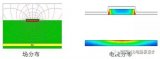

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽

2023-05-22 09:15

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

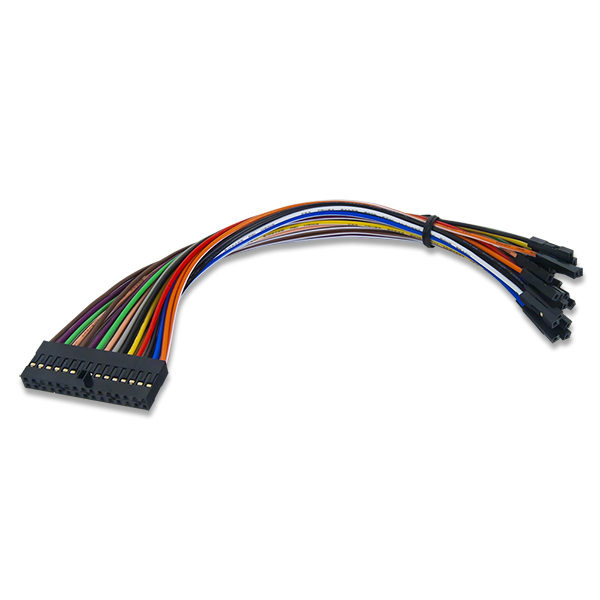

Analog Discovery信号线组件,或称Flywire,是与Analog Discovery产品原装信号线相同的组件。

2019-11-26 11:08

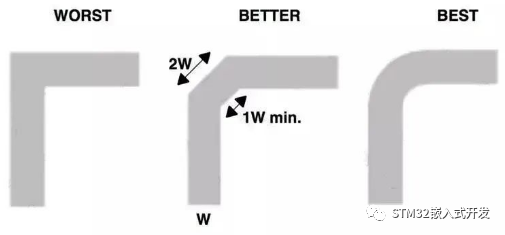

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直

2023-04-03 16:29

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线

2019-03-15 14:05

信号线主要是指在电气控制电路中用于传递传感信息与控制信息的线路。信号线往往以多条电缆线构成为一束或多束传输线,也可以是排列在印制板电路中的印制线,随着科技与应用的不断进

2019-05-20 15:35

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走

2018-03-08 17:18