约束流程 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源

2020-11-20 14:44

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。下面我们来看看这种源

2022-12-26 17:04

产生毛刺,且易受环境的影响,不利于器件的移植; 同步电路 1. 电路的核心逻辑是由各种各样的触发器实现的,所以比较容易使用寄存器的异步复位/置位端,以使整个电路有一个确定的初始状态; 2. 整个电路是由时钟沿驱动的; 3. 以触发器为主体的同步

2020-12-05 11:53

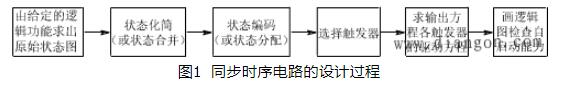

第二十七讲 同步时序逻辑电路的设计 7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步

2009-03-30 16:31

既然时序电路是有记忆功能地,那有几个概念必须是要清楚的:输入信号、输出信号、激励信号以及现态、次态及其转换关系。

2020-08-08 10:19

了解吗? (1)纯组合逻辑电路的缺点在哪? (3)纯组合逻辑电路完成不了什么功能? (2)为什么需要时钟和寄存器呢? 带着这三个疑问我们来认识一下时序逻辑电路。 二. 同步时序逻辑电路的作用 1.

2020-12-25 14:39

选定触发器的类型后,根据状态转换图(或状态转换表)和选定的状态编码,触发器的类型,写出电路的状态方程、驱动方程和输出方程。

2019-05-20 17:07

第二十二讲 同步时序逻辑电路的分析方法 内容提要7.1 概述一、时序电路的定义二、电路构成三、分类:1 同步2 异

2009-03-30 16:26

同步时序电路的延迟最常用的设计方法是用分频或者倍频的时钟或者同步计数器完成所需的延迟。

2018-07-13 17:59

从大学时代第一次接触FPGA至今已有10多年的时间,至今记得当初第一次在EDA实验平台上完成数字秒表、抢答器

2017-11-06 18:15