电子发烧友

7950次浏览

同步时序逻辑电路:本章系统的讲授同步时序逻辑电路的工作原理、分析方法和设计方法。从同步

2009-09-01 09:06

根据源同步的一些基本问题,在Cadence仿真环境下,对源同步时序进行仿真,仿真结果表明,设计能满足噪声容限和过冲,仿真后的可知数据线和时间的延时约为0.3ns,满足源同步

2012-05-29 15:26

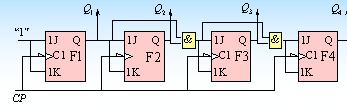

同步时序数字电路的分析二进制同步计数器 分析步骤: 1.确定电路是否是同步时序数字电路 2.确定触发器的驱动方程 3.做

2008-10-20 10:10

约束流程 说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源

2020-11-20 14:44

针对普通时钟系统存在着限制时钟频率的弊端,人们设计了一种新的时序系统,称之为源同步时序系统。它最大的优点就是大大提升了总线的速度,在理论上信号的传送可以不受传输延迟的影响。下面我们来看看这种源

2022-12-26 17:04

同步时序机状态加全模拟是同步时序机反设计的关键步骤。因时序机状态出现的频率不同,模拟分析的时间不等,有的太长,难以满足要

2009-08-29 10:06

提出了从状态转换图中直接求得触发器的置位和复位函数,从而确定触发器的驱动方程这样一种设计同步时序逻辑电路的新方法.设计原理简单,易于理解,适合于所有同步时序

2010-02-28 19:23

产生毛刺,且易受环境的影响,不利于器件的移植; 同步电路 1. 电路的核心逻辑是由各种各样的触发器实现的,所以比较容易使用寄存器的异步复位/置位端,以使整个电路有一个确定的初始状态; 2. 整个电路是由时钟沿驱动的; 3. 以触发器为主体的同步

2020-12-05 11:53

第二十七讲 同步时序逻辑电路的设计 7.5 同步时序逻辑电路的设计用SSI触发器16进制以内7.5.1 同步

2009-03-30 16:31