在现代高速电子设计中,电源完整性(Power Integrity,PI)问题已成为影响系统性能的关键因素之一。在电源完整性问题中,同步开关噪声(Simultaneous Switching

2024-09-12 15:39

FPGA上同步开关噪声的分析 概述 随着半导体技术的快速发展,近年来FPGA 的器件容量和输入输出的管脚数量都极大的增加了,例如StratixIV 器件,最大的

2010-04-12 15:09

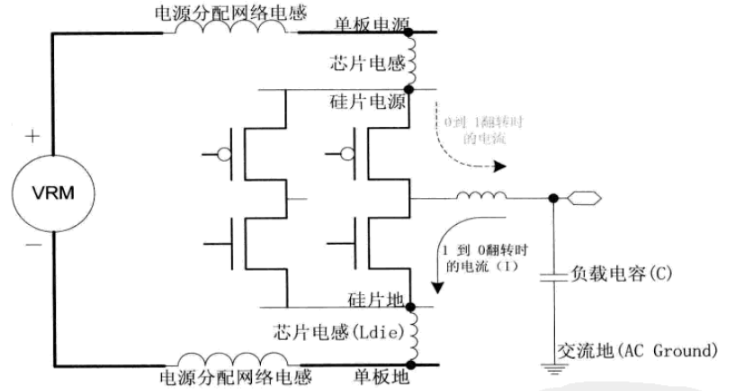

对于硬件设计人员来说,了解PDN的每个元件的谐振频率(例如,体旁路和去耦电容,平面电容和互连电感)及其对PI的影响非常重要。具有差的PI的PCB(例如,在50MHz及更高时具有高PDN阻抗)引起由PDN供电的信号的SSN和抖动。本文演示了PCB上PDN阻抗与SSN之间的关系。

2019-08-07 16:51

近年来,随着数字系统工作的时钟频率大大提高,数字IC 规模的扩大,PCB 板元件和布线密度的急剧增加,同步开关噪声对系统的影响也越来越明显,减小和抑制同步

2012-05-28 10:04

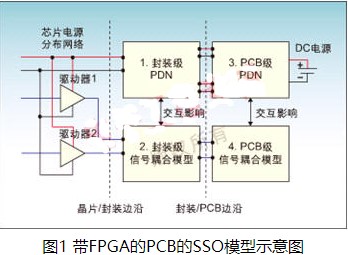

如今CMOS技术让一块FPGA器件可以拥有多个I/O接口。同时,近几年,低功耗已开始成为高速I/O接口的主流概念。降低功耗最有效的途径就是降低电压,而电压降低就会导致I/O接口所允许的噪声余量变小。因此,对FPGA用户而言,量化芯片、封装和PCB环境下的系统级同步

2019-05-16 08:00

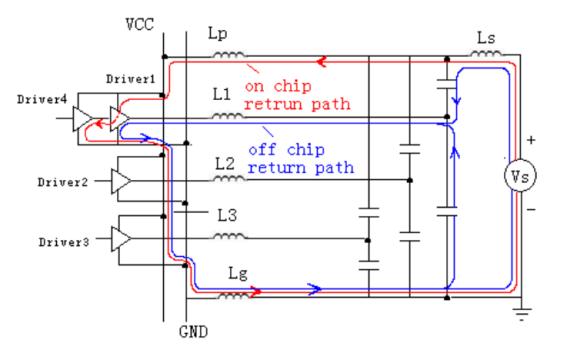

同步开关噪声(SSN)是指由于多个输出同时发生翻转而引起的感应噪声。

2020-09-14 14:43

近些年,随着信号速率的不断提升,测试对象出现了显著的变化,不再仅仅局限于传统的利用示波器测试信号波形,电源地噪声、同步开关噪声(SSN)、抖动(Jitter)逐渐成为互

2023-08-15 12:02

近些年,随着信号速率的不断提升,测试对象出现了显著的变化,不再仅仅局限于传统的利用示波器测试信号波形,电源地噪声、同步开关噪声(SSN)、抖动(Jitter)逐渐成为互

2023-08-09 14:35

德州仪器 (TI) 宣布推出一款带 4 通道分组式延迟的串行控制 16 通道恒流LED 驱动器,TLC59282 可通过对 LED 输出开关进行摆动处理来最大限度降低同步开关噪

2011-02-18 09:13

德州仪器 (TI)日前推出一款带 4 通道分组式延迟的串行控制 16 通道恒流LED 驱动器 TLC59282,该器件的最大特点是,分组式通道延迟(4通道一组)可最大限度地降低同步开关噪声

2011-03-31 10:35