电子发烧友

8798次浏览

在现代高速电子设计中,电源完整性(Power Integrity,PI)问题已成为影响系统性能的关键因素之一。在电源完整性问题中,同步开关噪声(Simultaneous Switching

2024-09-12 15:39

FPGA上同步开关噪声的分析 概述 随着半导体技术的快速发展,近年来FPGA 的器件容量和输入输出的管脚数量都极大的增加了,例如StratixIV 器件,最大的

2010-04-12 15:09

噪声SSN同步开关噪声Simultaneous Switch Noise,简称为SSN,代表的意思为大量的芯片同步切换时

2021-10-21 20:21

文中提出了一种应用于印刷电路板的新颖二维电磁带隙(MS-EBG)结构,其单位晶格由折线缝隙组合与正方形贴片桥接构成,以抑制同步开关噪声。结果表明,抑制深度为-30 dB时,与传统L-brid

2012-02-27 11:19

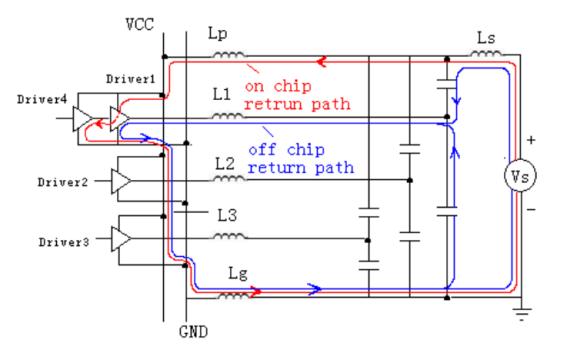

管脚。大量的输出管脚在同一时刻翻转会引起同步切换噪声。目前同步切换噪声是FPGA 领域的一个新的挑战。 同步切换

2020-04-27 08:00

摘要:提出了一种分析高速MCM电路系统中电源/接地板上同步开关噪声的方法,即基于部分元等效电路(PEEC)结合块缩减算法PRIMA和多端口网络(电源/接地板)的时域宏模型通过与平面

2010-05-15 09:37

摘要:本文针对抑制印刷电路板中电源平面与接地平面之间的同步开关噪声问题,提出了一种新型的二维电磁带隙结构(BS EBG)。其有效阻带为220 MHz~20 GHz,覆盖近20 GHz 的带宽

2018-09-28 16:18

对于硬件设计人员来说,了解PDN的每个元件的谐振频率(例如,体旁路和去耦电容,平面电容和互连电感)及其对PI的影响非常重要。具有差的PI的PCB(例如,在50MHz及更高时具有高PDN阻抗)引起由PDN供电的信号的SSN和抖动。本文演示了PCB上PDN阻抗与SSN之间的关系。

2019-08-07 16:51

近年来,随着数字系统工作的时钟频率大大提高,数字IC 规模的扩大,PCB 板元件和布线密度的急剧增加,同步开关噪声对系统的影响也越来越明显,减小和抑制同步

2012-05-28 10:04

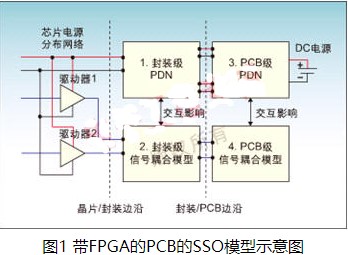

如今CMOS技术让一块FPGA器件可以拥有多个I/O接口。同时,近几年,低功耗已开始成为高速I/O接口的主流概念。降低功耗最有效的途径就是降低电压,而电压降低就会导致I/O接口所允许的噪声余量变小。因此,对FPGA用户而言,量化芯片、封装和PCB环境下的系统级同步

2019-05-16 08:00