项目中主要用到的原语与IO端口有关,所以基本在Input/Output Functions 和IO两类中。下面着重介绍实际中所用到的几个原语,芯片A7系列。

2019-01-06 11:23

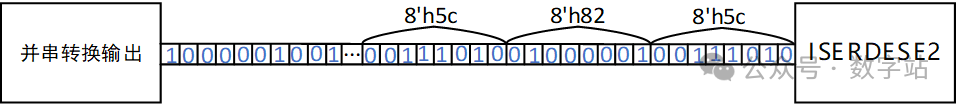

前面在讲解HDMI接口之前,讲解过IDDR、ODDR、OSERDESE2、IBUF等原语,之后一直有读者在问什么时候更新ISERDESE2这个原语。前文讲解过这些原语都在HDMI或者RGMII中使用过,但是ISERD

2025-03-17 10:52

Xilinx公司的原语按照功能分为10类,包括:计算组件、I/O端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。下面分别对其进行详细介绍。

2022-02-08 14:01

UltraRAM 原语(也称为 URAM)可在 Xilinx UltraScale +™ 架构中使用,而且可用来高效地实现大容量深存储器。

2019-07-13 11:08

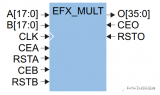

在使用Trion乘法器可能会遇到以下问题: (1)[EFX-0652 ERROR] 'EFX_MULT' instance 'mult' port 'CEA' is not permanently disabled in the Register Bypass mode. 说明:如果输 入寄存器A_REG没有使能,CEA接口要设置为0 (2)[EFX-0652 ERR OR] 'EFX_MULT' instance 'mult' port 'RSTA' is not permanently disabled in the Register Bypass mode. 说明:如果输 入寄存器A_REG没有使能,RSTA接口要设置为0 (3)[EFX -0652 ERROR] 'EFX_MULT' instance 'mult' port 'CLK' is not permanently disabled in the Register Bypass mode. 说明:如果 输入和输出寄

2024-05-20 16:35

在前一章中,我们介绍了Verilog HDL提供的内置基本门。本章讲述Verilog HDL指定用户定义原语U D P的能力。

2022-08-08 11:46

如果普通的GPIO怎么走全局时钟网络,其实很简单,打开原主文档,找到EFX_GBUFCE,该部分提供了verilog和VHDL的用法。

2023-04-06 11:44

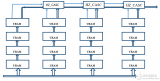

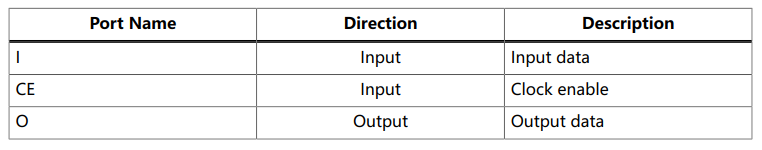

OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。

2019-02-17 10:55

对于前端设计人员,经常会需要一个MUX来对工作模式,数据路径进行明确(explicit)的声明,这个对于中后端工程师下约束也很重要。这里介绍一种巧用的RTL原语,实现MUX的方法。

2023-12-14 16:26

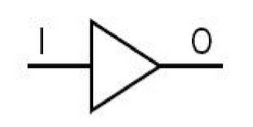

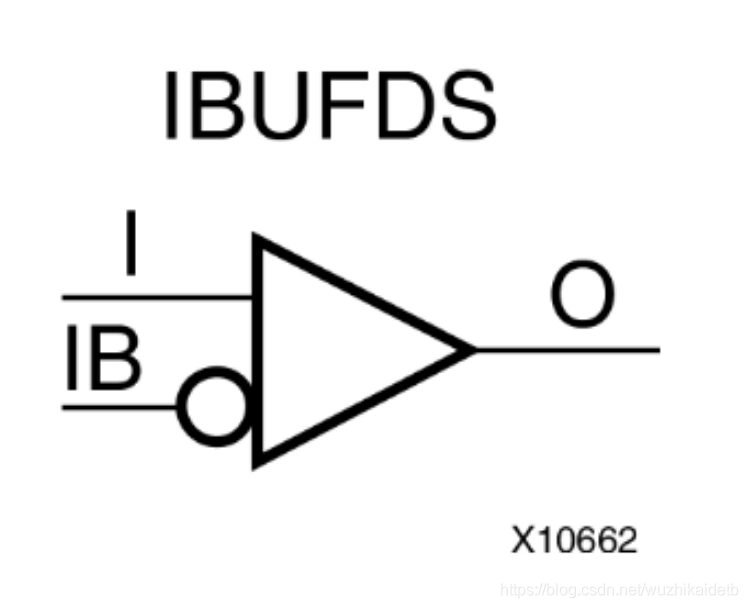

IBUFDS、和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 用于差分输入,OBUFDS用于差分输出。

2022-02-16 16:21