CORE Generator里有很多的IP核,适合用于各方面的设计。一般来说,它包括了:基本模块,通信与网络模块,数字信号处理模块,数字功能设计模块,存储器模块,微处理器,控制器与外设,标准与协议设计模块,语音处理模块,标准总线模块,视频与图像处理模块等。

2022-06-20 17:21

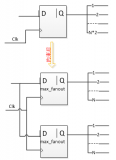

注意get_cells选中的必须是要求编译器复制它来降低扇出的寄存器,因为verilog代码里面和最终实现的电路里面的寄存器名字很可能不一样,所以建议综合完成后在原理图里面去找到对应寄存器,然后复制他的名字,这样就不

2018-12-27 13:23

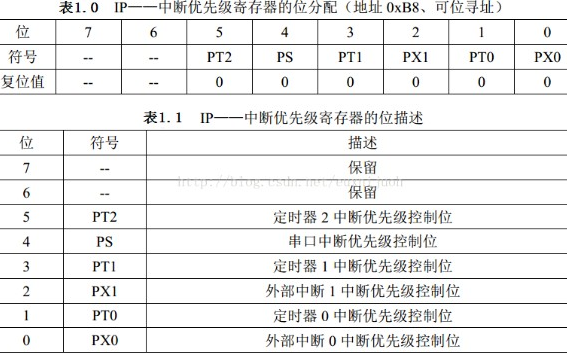

在讲中断产生背景的时候,我们仅仅讲了看电视和烧水的例子,但是实际生活当中还有更复杂的,比如我正在看电视,这个时候来电话了,我要进入接电话的“中断”程序当中去,就在接电话的同时,听到了水开的声音,水开的“中断”也发生了,我们就必须要放下手上的电话,先把煤气关掉,然后再回来听电话,最后听完了电话再看电视,这里就产生了一个优先级的问题。

2018-10-20 09:57

在高级电力电子系统中,升压模块的输出特性必须满足纹波电压小于1V的严格要求。

2023-10-13 16:13

应该有可以回答的上来的,但是大部分应该是回答不上来。标题的回答也不对。 计算机内存里面分这么几种数据 存在SRAM里面,嗯?内存?对也不对,大家觉得内存条应该很快了吧?不,不快。 我的电脑里面有三种

2024-06-04 10:28

有时候网表中可能会有一些空的module(在网表中体现为Module下面没有Cell或者准确说没有含MOS管的有效器件),而它们在版图里面也是不存在的,因此LVS的时候会报source里面能找到,但是版图里面没有找到

2023-05-24 09:47

目前集成电路的封装内部最常见的方式有「打线封装(Wire bonding)」与「覆晶封装(FCP:Flip Chip Package)」两种,如果芯片的正面朝上,也就是含有黏着垫的那一面朝上,通常使用「打线封装(Wafer bonding)

2023-10-25 15:59

打标效率最高,有时会出现衔接线、不均匀问题,打标细的的图形、字体时,不会出现上述问题, 所以弓形填充为首选。

2019-12-28 11:42

分析一个STM32的小开发板的设计: 先看2D的预览 底面 多个电容来滤波 一个晶振提供时基 就是长这样 这个是提供一个复位电平 原理图里面都是使用的网络标签,在原理图里面只要一个引脚的名字

2023-05-16 09:51

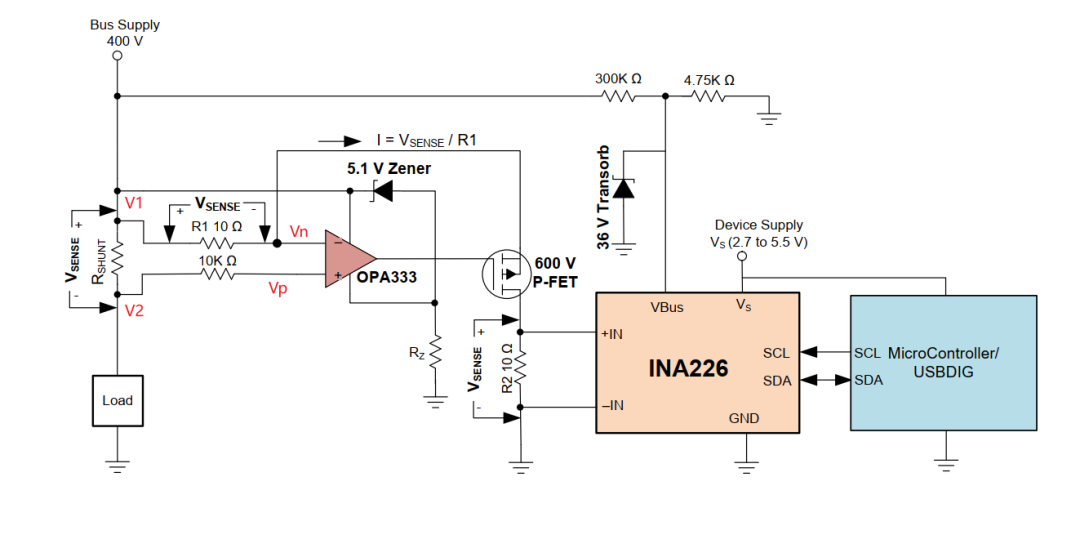

今天在群里看到了一张图,是TI的一个40V~400V非隔离型的高端电流检测方案的一个原理框图,这个图里,比较有意思的一点就是巧妙的利用了稳压二极管改变了运算放大器的共模输入电压范围 。主要使用了一个OPA333,一个高压PMOS,还有一个INA226。

2023-12-06 16:11