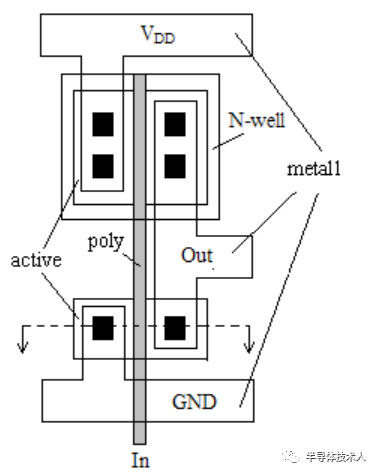

CMOS 集成电路的基础工艺之一就是双阱工艺,它包括两个区域,即n-MOS和p-MOS 有源区

2022-11-14 09:34

CMOS工艺是在PMOS和NMOS工艺基础上发展起来的。

2023-07-06 14:25

CMOS 集成电路的基础工艺之一就是双阱工艺,它包括两个区域,即n-MOS和p-MOS 有源区,分別对应p

2022-11-14 09:32

与亚微米工艺类似,双阱工艺是指形成NW和PW的工艺,NMOS 是制造在PW里的,PMOS是制造在NW里的。它的目的是形成PN 结隔离,使器件之间形成电性隔离,优化晶体管

2024-11-04 15:31

近年来,有关将CMOS工艺在射频(RF)技术中应用的可能性的研究大量增多。深亚微米技术允许CMOS电路的工作频率超过1GHz,这无疑推动了集成

2012-05-21 10:06

本文主要介绍CMOS集成电路基本制造工艺,特别聚焦于0.18μm工艺节点及其前后的变化,分述如下:前段工序(FrontEnd);0.18μmCMOS前段工序详解;0.1

2025-03-20 14:12

Pre-CMOS/MEMS 是指部分或全部的 MEMS 结构在制作 CMOS 之前完成,带有MEMS 微结构部分的硅片可以作为 CMOS 工艺的初始材料。

2022-10-13 14:52

在下面的图中较为详细的显示了堆叠式DRAM单元STI和阱区形成工艺。下图(a)为AA层版图,虚线表示横截面位置。

2023-09-04 09:32

Doping Well)技术作为一种精密的掺杂方法,对于实现高性能和高密度的集成电路至关重要。倒掺杂阱工艺通过精确控制掺杂深度和横向扩散,有效改善了闩锁效应和DIBL(drain induced barrier l

2025-01-03 14:01

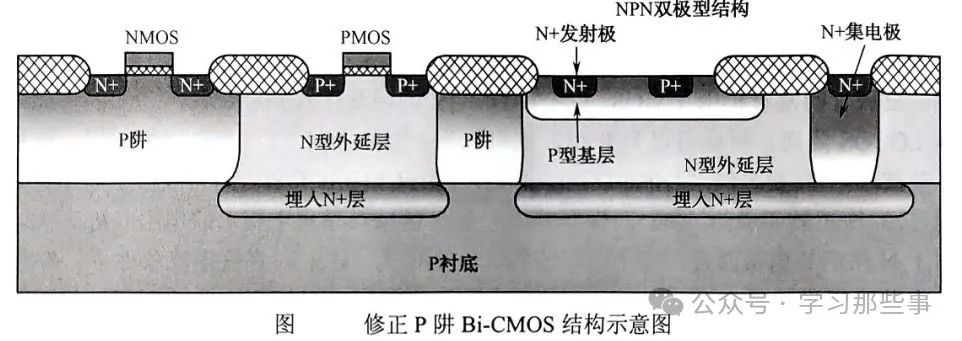

Bi-CMOS工艺将双极型器件(Bipolar)与CMOS工艺结合,旨在融合两者的优势。CMOS具有低功耗、高噪声容限、

2025-03-21 14:21