分析电网调度运行管理系统的工作特点,根据系统内不同任务分工协作的要求,利用多Agent 技术将系统划分成不同功能的模块。提出了基于多Agent 的CSCW 环境下的一种电网调度协同工作

2011-05-28 10:57

电子发烧友网站提供《三个传感器协同工作的智能狗碗.zip》资料免费下载

2022-11-17 10:28

电子发烧友网为你提供集成智能照明如何与其他系统协同工作?资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-04-17 08:53

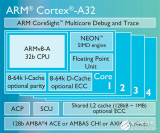

谈论资源丰富的单片机与微小、电池供电的应用空间可穿戴设备协同工作,似乎是自相矛盾的说法。但是ARM致力于使用最近发布的Cortex-A32处理器来解决这种矛盾。将处理器体系结构和工艺技术结合

2017-10-12 11:01

设计挑战是:如何最高效率地实现ARM和DSP或协处理器的通信和协同工作?本文将详细为您介绍解决这一技术挑战的解决方案和实现指南。 德州仪器(TI)的第一颗达芬奇(DaVinci)芯片(处理器)DM6?46已经问世快三年了。继DM6?4x之后,TI又陆续推

2017-10-25 14:35

介绍了一种由三个DSP嵌入式子系统构成的基于CAN总线的分布式系统。该系统具有多路信号实时处理、过程控制、与外部测控中心实时交互等功能。

2010-11-19 15:06

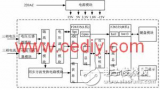

影响系统整体性能。为弥补这一缺点,本设计提出了采用DSP+ DRAM+DSP的双处理器协同工作模式,一片DSP全权负责采集、捕获工作,另一片负责数据处理和人机对话,这样可实现不间断、高速度、多端口的处理。针对通信双方速度不匹配、信息交换实时性要

2017-10-25 14:24

写在前面:STM32MP157是ST进军Linux的首款微处理器,采用MCU+MPU的组合,集成两颗主频微800MHz的Cortex-A7应用处理器内核(支持开源linux操作系统),和一颗主频微209M的Cortex-M4微控制器内核(完美沿用现有的STM32 MCU生态系统),既充分满足多种应用的灵活性需求,又实现了最佳性能和低功耗特性,还支持3D图形处理单元(3D GPU)。那STM32MP1系列,A7和M4是如何进行通信的呢?简单的说,A7和M4两个核心的通信,是通过底层的IPCC控制器

2021-12-01 12:51

为了整合区域化制造企业间的资源以实现资源共享和协同工作,参考网格的运行机制,搭建了制造网格资源共享服务平台,设计了该平台的资源共享管理系统、协同工作系统和运

2009-08-25 14:25

本帖最后由 jinyi7016 于 2016-10-19 14:49 编辑 感谢电子民烧友与锆石提供的这次试用机会。本人在此之前还从未使用过任何的FPGA产品,所以此次试用也是从零学起。首先是锆石的教程,真是入门的不二选择。可以这么快的小窥FPGA的门径,也是多亏了锆石的各种教程。我不仅仅是试用了一款开发板,更是学到了一种技术,对我而言一种全新的技术。锆石的教程与例程都是非常的丰富,一方面是方便的学习,但也一方便使学习者变得懒惰了。所有工程都打开就好了,这里我都是从头新建的工程,把一切的流程全都自己走一便,尽管是简单的新建工程也是。这样,既可以熟悉软件的使用,也可以在流程中对FPGA有更深的认识。FPGA有着及其丰富的应用环境,从工业品到消费品都可以找到FPGA的影子。但对于我而言,还是要用到工业上。用其实现各种功能当然是很好的,但是我又是一个ARM与DSP的开发工程师,将这三都结合起来,看上去是更有意义的。所以就产生了这次试用的项目。模拟一种资源竞争的情况下,使用FPGA来管理STM32与DSP2812不会存在同时访问同一资源。比如共用一片SD卡,共用一片外部RAM或FLASH等等,都会存在竞争关系,即不可以同时访问这些资源。还有就是在PCB面积有限的情况下,又要使用大量的逻辑器件,如几片138,几片非门,几片与门之类的,PCB上放不下,产品尺寸又不能调整,那就只能用一片FPAG(或CPLD)了。虽然学习使用了Qsys,但是在这样的项目中,使用Qsys与使用一片单片机也没有什么区别,所以这里不使用Qsys,单纯使用硬件语言。由于手头资源有限,也为了可以直观的看的运行结果,现以PC上的串口为要竞争的公共资源。STM32与DSP都要通过这个串口,向PC发送数据,但是一条总线上若是有两个设备同时在发收,总线势必会乱掉了,这时就要使用FPGA来调节了。系统结构图如下:如图,在没有FPGA时,同时给两个开发板上电,PC的串口助手上收不到数据,但是在断电时收到的却是乱码。STM32的串口2使用9600波特率,偶校验方式进行通讯。void USART2_Config(void){USART_InitTypeDef USART_InitStructure;GPIO_InitTypeDef GPIO_InitStructure;NVIC_InitTypeDef NVIC_InitStructure;GPIO_InitStructure.GPIO_Pin = GPIO_Pin_3;GPIO_InitStructure.GPIO_Mode =GPIO_Mode_IN_FLOATING;GPIO_Init(GPIOA, &GPIO_InitStructure); GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;GPIO_Init(GPIOA, &GPIO_InitStructure);USART_InitStructure.USART_BaudRate = 9600;USART_InitStructure.USART_WordLength = USART_WordLength_9b;USART_InitStructure.USART_StopBits = USART_StopBits_1;USART_InitStructure.USART_Parity = USART_Parity_Even;//偶USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None;USART_InitStructure.USART_Mode = USART_Mode_Rx | USART_Mode_Tx;USART_Init(USART2, &USART_InitStructure);USART_ITConfig(USART2, USART_IT_RXNE, ENABLE);USART_Cmd(USART2, ENABLE);NVIC_InitStructure.NVIC_IRQChannel = USART2_IRQn;NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 1;NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);}DSP串口配置程序void InitScic(void){ EALLOW;GpioCtrlRegs.GPBPUD.bit.GPIO62 = 0; GpioCtrlRegs.GPBPUD.bit.GPIO63 = 0;GpioCtrlRegs.GPBQSEL2.bit.GPIO62 = 3;GpioCtrlRegs.GPBMUX2.bit.GPIO62 = 1;GpioCtrlRegs.GPBMUX2.bit.GPIO63 = 1;ScicRegs.SCICCR.all =0x0007; ScicRegs.SCICTL1.all =0x0003;ScicRegs.SCICTL2.bit.TXINTENA =1;ScicRegs.SCICTL2.bit.RXBKINTENA =1;ScicRegs.SCIHBAUD =0x0000;ScicRegs.SCILBAUD =0x0027; ScicRegs.SCICCR.bit.LOOPBKENA =0;ScicRegs.SCICTL1.all =0x0023; PieVectTable.SCIRXINTC = &scicRxFifoIsr;PieVectTable.SCITXINTC = &scicTxFifoIsr;EDIS;}STM32以9600,偶校验每秒发关两次,字符依次为1、2、3、4、5;DSP以115200,无校验发送,每秒发关一次,字符依次为A、B、C、D、E;当FPGA接收到了一定量的数据就会以115200波特率发送到PC机的串口中,如下图。FPGA程序如下:module A4_Uart_Top(//输入端口CLK_50M,RST_N,UART_RX,UART_RX_DSP,UART_RX_ST,//输出端口UART_TX,UART_TX_DSP,UART_TX_ST);inputCLK_50M; inputRST_N; inputUART_RX; outputUART_TX; inputUART_RX_DSP; outputUART_TX_DSP;inputUART_RX_ST; outputUART_TX_ST;wirerx_bps_start;wiretx_bps_start;wirerx_bps_flag;wiretx_bps_flag;wire[7:0]out_rx_data;wire[7:0]out_tx_data;wirerx_bps_dsp_start;wiretx_bps_dsp_start;wirerx_bps_dsp_flag;wiretx_bps_dsp_flag;wire[7:0]out_rx_dsp_data;wire[7:0]out_tx_dsp_data;wirerx_bps_st_start;wiretx_bps_st_start;wirerx_bps_st_flag;wiretx_bps_st_flag;wire[7:0]out_rx_st_data;wire[7:0]out_tx_st_data;Uart_Bps_Module Uart_Rx_Bps_Init(.CLK_50M(CLK_50M ),.RST_N(RST_N),.bps_start(rx_bps_start),.bps_flag(rx_bps_flag));Uart_Rx_ModuleUart_Rx_Init( .CLK_50M(CLK_50M ),.RST_N(RST_N),.UART_RX(UART_RX ),.rx_bps_start (rx_bps_start),.rx_bps_flag (rx_bps_flag),.out_rx_data (out_rx_data));Uart_Bps_Module Uart_Tx_Bps_Init(.CLK_50M(CLK_50M ),.RST_N(RST_N),.bps_start(tx_bps_start),.bps_flag(tx_bps_flag));Uart_Tx_ModuleUart_Tx_Init( .CLK_50M(CLK_50M ),.RST_N(RST_N), .UART_TX(UART_TX ),.tx_bps_start (tx_bps_start),.tx_bps_flag (tx_bps_flag),.tx_start_flag (rx_bps_start),.in_rx_data(out_rx_dsp_data),.out_tx_data(out_tx_data),);Uart_Bps_Module Uart_Rx_DSP_Bps_Init(.CLK_50M(CLK_50M ),.RST_N(RST_N),.bps_start(rx_bps_dsp_start),.bps_flag(rx_bps_dsp_flag));Uart_Rx_ModuleUart_Rx_DSP_Init( .CLK_50M(CLK_50M ),.RST_N(RST_N),.UART_RX(UART_RX_DSP ),.rx_bps_start (rx_bps_dsp_start),.rx_bps_flag (rx_bps_dsp_flag),.in_rx_data(out_rx_dsp_data),);Uart_Bps_Module Uart_Tx_DSP_Bps_Init(.CLK_50M(CLK_50M ),.RST_N(RST_N),.bps_start(tx_bps_dsp_start),.bps_flag(tx_bps_dsp_flag));Uart_Tx_ModuleUart_Tx_DSP_Init( .CLK_50M(CLK_50M ),.RST_N(RST_N), .UART_TX(UART_TX_DSP ),.tx_bps_start (tx_bps_dsp_start),.tx_bps_flag (tx_bps_dsp_flag),.tx_start_flag (rx_bps_dsp_start),.in_rx_data(out_rx_dsp_data),.out_tx_data(out_tx_dsp_data), );Uart_Bps_Module Uart_Rx_ST_Bps_Init(.CLK_50M(CLK_50M ),.RST_N(RST_N),.bps_start(rx_bps_dsp_start),.bps_flag(rx_bps_dsp_flag));Uart_Rx_ModuleUart_Rx_ST_Init( .CLK_50M(CLK_50M ),.RST_N(RST_N),.UART_RX(UART_RX_ST ),.rx_bps_start (rx_bps_st_start),.rx_bps_flag (rx_bps_st_flag),.out_rx_data (out_rx_st_data));Uart_Bps_Module Uart_Tx_ST_Bps_Init(.CLK_50M(CLK_50M ),.RST_N(RST_N),.bps_start(tx_bps_st_start),.bps_flag(tx_bps_st_flag));Uart_Tx_ModuleUart_Tx_ST_Init( .CLK_50M(CLK_50M ),.RST_N(RST_N), .UART_TX(UART_TX_ST ),.tx_bps_start (tx_bps_st_start),.tx_bps_flag (tx_bps_st_flag),.tx_start_flag (rx_bps_st_start),.in_rx_data(out_rx_st_data),.out_tx_data(out_tx_st_data),);endmodule硬件如下图,DSP板是自己打样的开发板,只焊接了必要的元件。本次项目基本完成。最后,再次感谢电子民烧友与锆石提供的这次试用机会。

2016-10-18 23:26