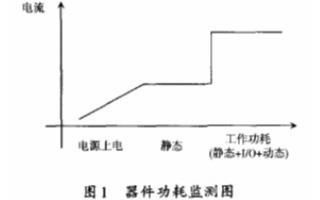

功耗一般由两部分组成:静态功耗和动态功耗。静态功耗也称为待机功耗,是指逻

2020-01-16 09:46

DPS就是一个在需要时启用电子元件、在不需要时禁用电子元件的动态过程。图1所示为一个典型的基于SAR型ADC的数据采集子系统。

2018-03-23 15:11

CMOS电路中的功耗分为两部分:静态功耗和动态功耗;

2024-01-16 09:39

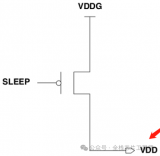

SoC中CMOS电路功耗有:一是静态功耗,主要是由静电流、漏电流等因素造成的;二是动态功耗,主要是由电路中信号变换时造成的瞬态开路电流(crowbar current)

2018-02-12 17:31

PTPX,是基于PT,对全芯片进行power静态和动态功耗分析的工具。包括门级的平均功耗和峰值功耗。可以说PTPX就是PT工具的一个附加工具。

2022-10-24 16:55

多阈值工艺(Multi-Vt Design)方法:这种方法是通过使用不同阈值电压的标准单元来降低静态功耗和动态功耗。对于性能要求高的模块,可以使用低阈值单元,提高速度;对于性能要求低的模块,可以使用高阈值单元,降低漏

2023-08-20 11:20

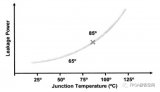

总的来说,芯片进入40nm时代后,门槛电压的降低以及晶体管尺寸的减小,都将会导致芯片漏电流增加,而这个漏电流就成为芯片静态功耗的主要来源,有的甚至高于芯片工作的动态功耗。 新工艺的使用反而

2018-01-26 10:55

赛灵思 ISE 12设计套件利用智能时钟门控技术将动态功耗降低30% 1)赛灵思今天要宣布什么消息? ISE® 12设计套件不仅实现了功耗与成本的突破性优化,而且为逻辑、嵌入式、DSP和系统设计人

2018-07-02 06:20

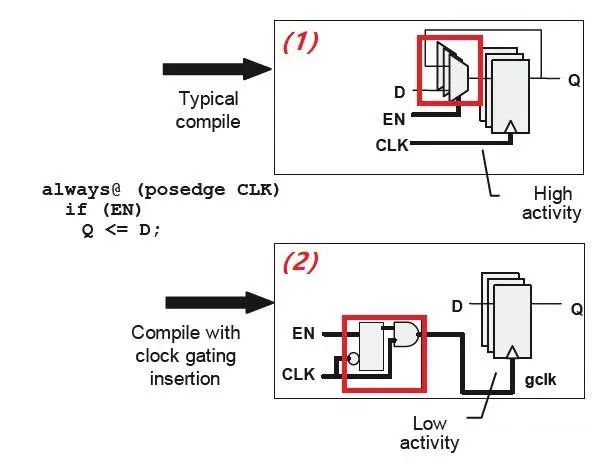

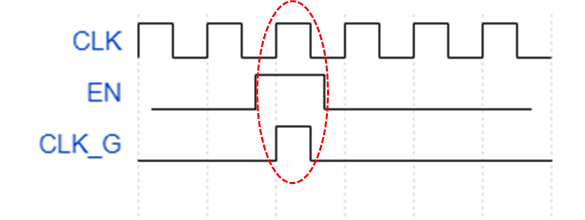

当寄存器组的输出端没有驱动或没有变化时,可以关掉寄存器组的时钟来减少动态功耗,此谓门控时钟 (Clock Gating, CG) 技术。

2023-03-29 11:37

芯片中大部分的动态功耗消耗在时钟网络中。这是由于时钟树上的单元(cells)有较高的翻转率、驱动能力较大且数量较多所导致的。

2023-12-01 14:50