当RTL代码修改较少时,使用增量编译功能可以提高工程的编译速度,Incremental Compile增量编译是Vivado

2019-01-22 17:27

通常情况下,一旦创建好Vivado工程,添加了相应的RTL文件,Vivado会自动找到设计的顶层文件,正确地显示设计层次。在这个过程中,Vivado会自动分析文件的编译

2023-01-06 09:27

随着FPGA规模的增大,设计复杂度的增加,Vivado编译时间成为一个不可回避的话题。尤其是一些基于SSI芯片的设计,如VU9P/VU13P/VU19P等,布局布线时间更是显著增加。当然,对于一些设计而言,十几个小时是合理的。但我们依然试图分析设计存在的问题以期缩

2024-09-18 10:43

Incremental Compile增量编译是Vivado提供的一项高阶功能。目的旨在当设计微小的改变时,重用综合和布局布线的结果,缩短编译时间。

2018-07-05 06:06

Xilinx Vivado开发环境编译HDL时,对时钟信号设置了编译规则,如果时钟由于硬件设计原因分配到了普通IO上,而非_SRCC或者_MRCC专用时钟管脚上时,编译

2024-04-15 11:38

程序员做软件开发,比较讨厌一件事,那就是编译代码速度很慢的问题。 尤其是C/C++代码,编码一分钟,编译一小时钟,这谁能受的了?

2023-07-06 10:53

今天就来说说嵌入式软件开发中,常见的提高编译速度的一些操作或者方法。

2022-03-09 17:31

在linux系统上实现vivado调用VCS仿真教程 作用:vivado调用VCS仿真可以加快工程的仿真和调试,提高效率。 前期准备:确认安装vivado软件和VCS软

2018-07-05 03:30

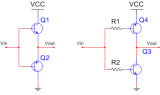

在做信号控制以及驱动时,为了加快控制速度,经常要使用推挽电路。推挽电路可以由两种结构组成:上P下N,上N下P。其原理图分别如下所示。

2023-05-17 09:33

今天发布一个Vivado 下固化 FLASH的压缩和提高加载速度的技巧和方法。这个方法对于需要快速加载程序的场合特别有用比如PCIE 需要满足200MS的加载时间才能实现上电后系统能够识别到开发板。

2019-04-20 10:39