关于Vivado Dashboard的功能可阅读这篇文章(Vivado 2018.3这个Gadget你用了吗)Vivado 2019.1的Dashboard功能进一步增

2019-06-12 14:49

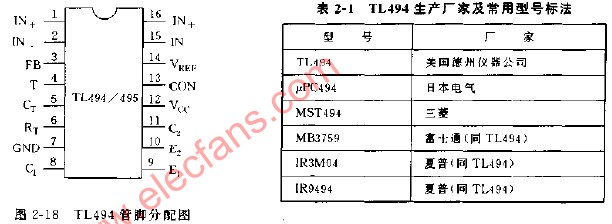

TL494管脚分配图

2009-10-14 16:21

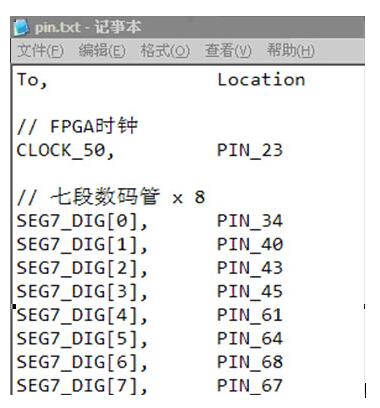

将Quartus II中FPGA管脚的分配及保存方法做一个汇总。本文首先介绍了FPGA 的管脚分配方法,其次介绍了Quartus II自动添加

2018-05-16 11:44

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从

2017-11-25 07:38

vivado有project模式和non-project模式,project模式就是我们常用的方式,在vivado里面新建工程,通过GUI界面去操作;non-project模式就是纯粹通过tcl来指定vivado的流

2022-10-17 10:09

设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚

2017-02-11 03:48

尽管 Vivado HLS支持C、C++和System C,但支持力度是不一样的。在v2017.4版本ug871 第56页有如下描述。可见,当设计中如果使用到任意精度的数据类型时,采用C++ 和System C 是可以使用Vivado HLS的调试环境的,但是C

2019-07-29 11:07

时序分析在FPGA设计中是分析工程很重要的手段,时序分析的原理和相关的公式小编在这里不再介绍,这篇文章是小编在练习Vivado软件时序分析的笔记,小编这里使用的是18.1版本的Vivado。 这次

2019-09-15 16:38

在Vivado中新建IO Planning工程来初步引脚分配,这样会大大提高开发效率 在这里,你可以选择最右侧的开发板型号,也可以选择Part,具体的FPGA的型号,选择完后,我们可以很清晰的看到该型号的资源列表:包括IO数、可用的IO数、内部BRAM大小、时钟

2018-10-22 17:12

在STM32的数据手册的管脚分配图中可以看到:PC14与OSC32_IN公用一个引脚,PC15与OSC32_OUT公用一个引脚,管脚配置如图1、图2、图3所示。它们的使用方法如下: 当LSE(低速

2017-12-04 16:55