与门真值表和与非门真值表的区别,与门真值表:有0出0,全1出1。与非门真值表:有0出1,全1出0。

2018-01-30 15:37

表征逻辑事件输入和输出之间全部可能状态的表格。列出命题公式真假值的表。通常以1表示真,0 表示假。命题公式的取值由组成命题公式的命题变元的取值和命题联结词决定,命题联结词的真值表给出了真假值的算法。

2018-01-30 15:16

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,多个一位全加器进行级联可以得到多位。全加器是形成三

2021-06-29 09:14

使用如ADI公司提供的高精度、低噪声、高速A/D转换器,例如用于ADMX3652模块中的器件,这类芯片专为高分辨率测量系统设计,能够满足六位半电压测量所需的精度指标。

2024-03-13 14:36

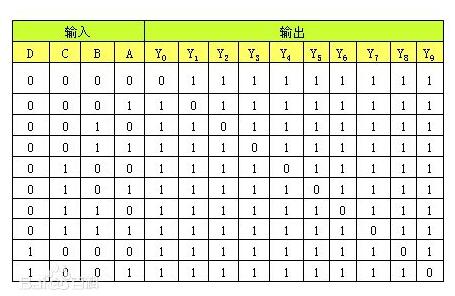

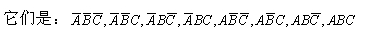

本文主要介绍了逻辑真值表怎么列出的_真值表是怎么画出来的。一个逻辑函数的卡诺图就是将此函数的最小项表达式中的各最小项相应地填入一个特定的方格图内,此方格图称为卡诺图。由A、B、C三个逻辑变量构成

2018-04-09 11:45

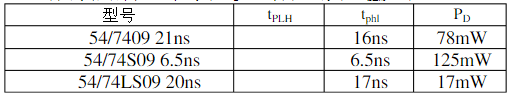

本文主要介绍了74ls09引脚图及功能表_真值表和特性参数。74ls09为集电极开路输出的四组2输入端与门(正逻辑),共有54/7409、54/74S09、54/74LS09三种线路结构型式,引出端符号:1A-4A

2018-04-09 10:09

74hc164是高速硅门CMOS电路,管脚与低功耗肖特基TTL(LSTTL)系列兼容。74hc164是8位的串入并出、边沿触发的移位寄存器,串入数据由DSA、DSB输入, 在每个时钟CP的上升沿数据

2017-10-27 15:59

半加器、全加器是组合电路中的基本元器件,也是CPU中处理加法运算的核心,理解、掌握并熟练应用是硬件课程的最基本要求。

2018-07-25 14:39

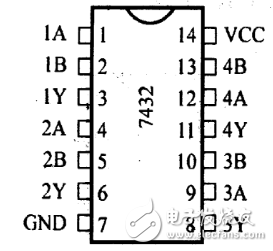

本文主要介绍了74ls32引脚图及功能真值表和特性参数。74LS32器件包含4路独立的2输入或门。74LS32的逻辑功能表达式为:Y=/(A·B)或Y=A+B,正逻辑。引出端符号:1A-4A 输入端、1B-4B

2018-04-09 14:37