全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。

2018-07-25 16:03

加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器。

2018-07-25 11:15

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,多个一位全加器进

2021-06-29 09:14

此篇文章里,我们将通过使用InTime来检验Vivado 2017.1和Vivado2016.4之间的性能对比。 概要:分别进行了3个Vivado 2017.1对Vivado

2018-07-04 11:23

半加器(Half Adder)和全加器(Full Adder)是数字电路中的基本组件,用于执行二进制加法运算。它们的主要区别在于功能和输入输出的数量。 1. 功能差异 半加器 : 半加器只能处理两个

2024-10-18 11:12

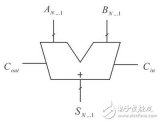

N位全加器将{AN,……,A1}、{BN,……,B1}和进位输入Cin作为输入,计算得到和{SN,……,S1}以及最高位的进位输出Cout(见图1)。每一位得到的和与进位输出都直接受其上一位的影响,其进位输出也会影响下一位。最终,整个全加器的和与输出都受进位输入C

2018-06-08 10:24

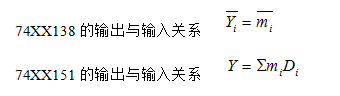

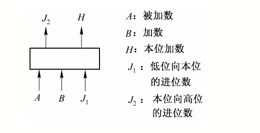

本文主要介绍了用74ls151实现全加器设计电路。根据全加器的定义可知:输入为:A,B,Ci其中A,B为被加数和加数,Ci为低位进位数。输出为:S,Co,其中S为本位和数,Co为高位进位数。其逻辑关系为:S=A⊕B⊕Ci;Co=AB+(A⊕B)Ci。

2018-05-07 09:52

Vivado可以导出脚本,保存创建工程的相关命令和配置,并可以在需要的时候使用脚本重建Vivado工程。脚本通常只有KB级别大小,远远小于工程打包文件的大小,因此便于备份和版本管理。下面把前述脚本升级到Vivado

2022-08-02 10:10

全加器是一个能够完成一位(二进制)数相加的部件。我们先来看一下两个二进制数的加法运算是怎样进行的。

2018-07-25 15:48

有时我们对时序约束进行了一些调整,希望能够快速看到对应的时序报告,而又不希望重新布局布线。这时,我们可以打开布线后的dcp,直接在Vivado Tcl Console里输入更新后的时序约束。如果调整

2024-10-24 15:08