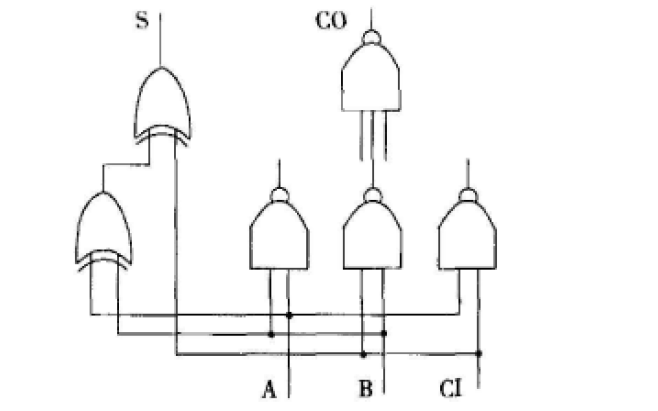

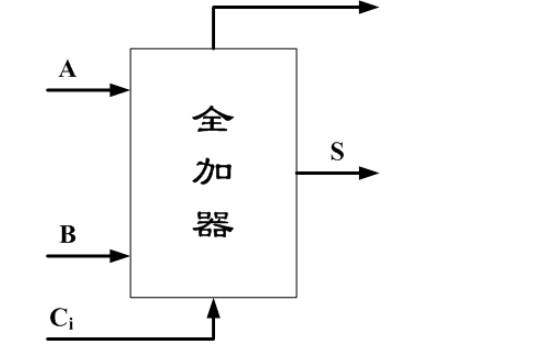

实验五 全加器、译码器及数码显示电路 一、实验目的 1、掌握全加器逻辑功能,熟悉集成加法器功能及其使用方法。 2、掌握用七段译码器和七段数码管显示十进制数的方法。 3、掌握

2012-07-16 23:01

Verilog数字系统设计四复杂组合逻辑实验2文章目录Verilog数字系统设计四前言一、什么是8位全加器和8为带超前进位的全加器?二、编程1.要求:2.门级原语实现8位全加器:3.门级原语实现带

2021-12-05 19:06

全加器是数字信号处理器微处理器中的重要单元,它不仅能完成加法,还能参与减法、乘法、除法等运算,所以,。提高全加器性能具有重要意义。本文分析了两种普通全加器,运用布尔代数对全加器

2019-07-03 17:11

FPGA学习的好资料,很实用的FPGA教程文档,快来学习吧。

2016-05-12 14:05

CC4008中文资料:型由具有段间快速超前进位的4个全加器段组成。

2008-04-07 22:27

本文档的主要内容详细介绍的是VHDL语言设计的全加器源代码和工程文件免费下载。

2019-06-03 08:00

摘要:应用CMOS电路开关级设计技术对超前进位全加器进行了设计,并用PSPICE模拟进行了功能验证.与传统门级设计电路相比,本文设计的超前进位电路使用了较少的MOS管,并能保持

2010-05-28 08:18

电子发烧友网站提供《在Spartan 6 FPGA上从头开始实现全加器.zip》资料免费下载

2023-06-15 10:13

多思计算机组成原理网络虚拟实验系统计算机组成原理实验一全加器实验

2021-10-22 10:36

基于单电子晶体管的I-V特性和传输晶体管的设计思想,用多栅单电子晶体管作为传输晶体管,设计了一个由5个SET构成的全加器,相对于静态互补逻辑设计的全加器,本文设计的全加器在器

2010-07-30 16:54