时钟是整个电路最重要、最特殊的信号,系统内大部分器件的动作都是在时钟的跳变沿上进行, 这就要求时钟信号时延差要非常小, 否则就可能造成时序逻辑状态出错。

2020-06-26 10:37

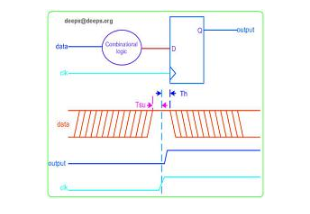

建立时间和保持时间是SOC设计中的两个重要概念。它们都与时序分析有关,是确保芯片正常工作的关键因素。

2023-08-23 09:44

输出电压保持时间是指当电源回路的输入部被停止供电后,输出电压的保持时间。微处理器或RAM等的Backup电路也是电压保持

2018-08-01 09:19

与电压之间存在一定的关系。在PWM信号周期内,占空比的变化会导致电平高电平时长的变化。当占空比较小时,高电平时长较短,对应的平均电压也相对较低;而当占空比较大时,高电平

2024-02-02 17:17

上次我们聊到了晶振的占空比,即信号在高电平持续时间与整个周期时间的比例。今天,我们来聊聊晶振频率信号中的脉冲、时钟周期和机械周期之间的

2024-07-17 14:38

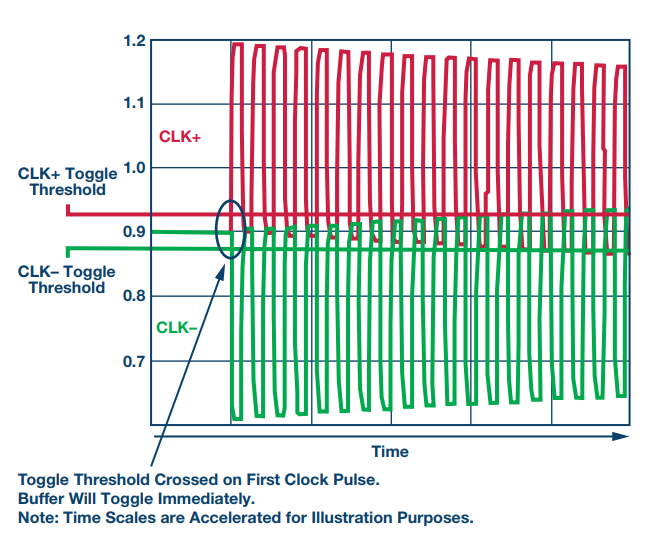

高速模数转换器(ADC)是定义上的器件 对模拟信号进行采样,因此必须具有采样时钟 输入。一些使用ADC的系统设计人员观察到速度较慢 比最初应用采样时钟时的预期启动时间长。 令人惊讶的是,这种延迟的原因往往是错误的启动

2023-01-05 11:07

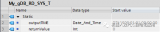

说明 可以使用该指令读取 CPU 时钟的当前日期和当前时间(模块时间)。 在此指令的 OUT 输出参数中输出读取的日期。得出的值不包含有关本地时区或夏令时的信息。 说明

2023-06-28 16:18

一个负载并联一个电容,电容的放电时间与电容量及负载电阻的大小有关,电容量越大,负载电阻的阻值越大,则电容的放电时间越长。下面我们以一个简单的电容放电电路为例,来详细介绍一下电容放电

2020-02-17 19:42

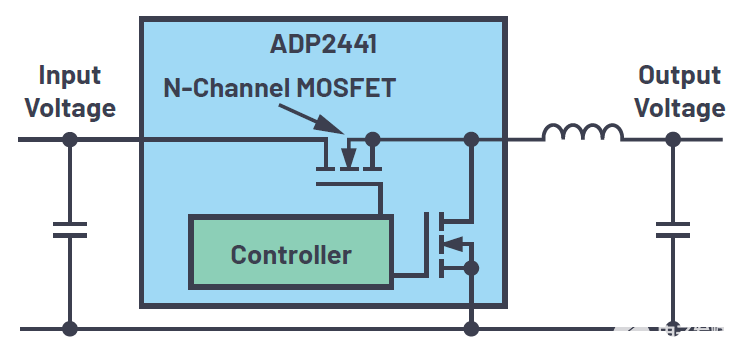

开关稳压器使用占空比来实现电压或电流反馈控制。占空比是导通时间(T上) 到整个周期长度,关断时间 (T关闭)加上导通时间

2022-12-20 14:18

我理解这个D触发正常运转要满足四个约束,第一个是建立时间,第二个是保持时间,第三个是对于最后一个传输门的关断时间的控制,第四个是[

2023-12-04 15:44