使用FPGA时序使时钟保持纯净或

2021-01-13 17:00

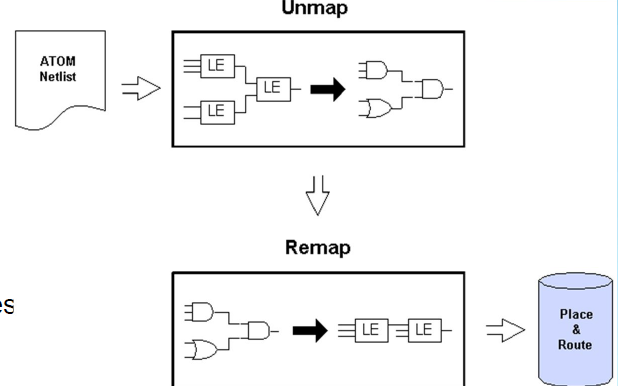

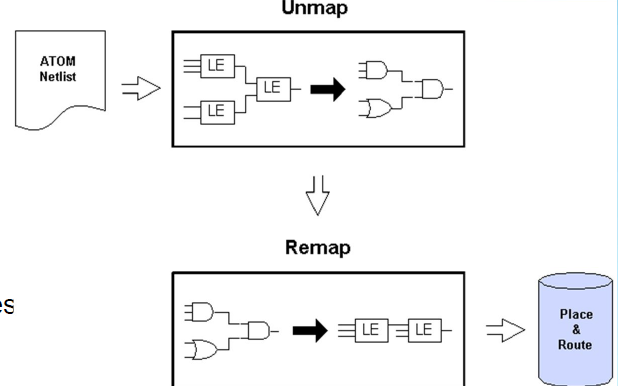

本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03

本文档的主要内容详细介绍的是FPGA的时序分析的优化策略详细说明。

2021-01-14 16:03

本文档的主要内容详细介绍的是Xilinx的时序设计与约束资料详细说明。

2021-01-14 16:26

本文档的主要内容详细介绍的是使用FPGA设计的2个实例详细说明包括了:Verilog HDL 设计练习一. 简单的组合逻辑设计,练习二. 简单时序逻辑电路的设计

2020-09-23 16:48

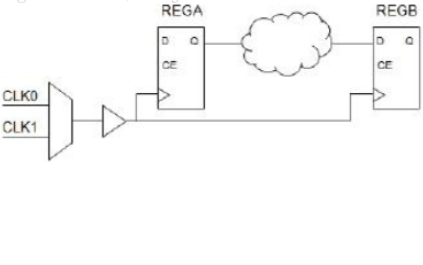

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。在

2020-11-10 13:53

在高速系统中FPGA时序约束不止包括内部时钟约束,还应包括完整的IO时序约束利序例外约束才能实现PCB板级的时序收敛。因

2021-01-13 17:13

本文档的主要内容详细介绍的是FPGA的入门基础知识详细说明。

2020-12-20 10:13

说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步是指

2021-01-11 17:46

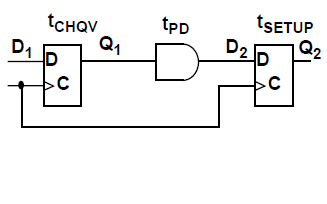

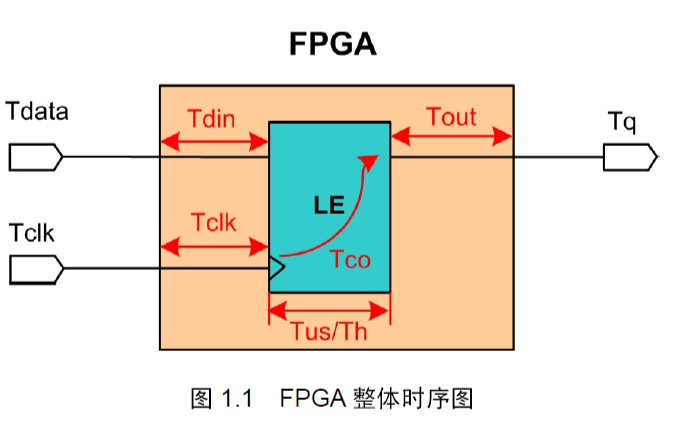

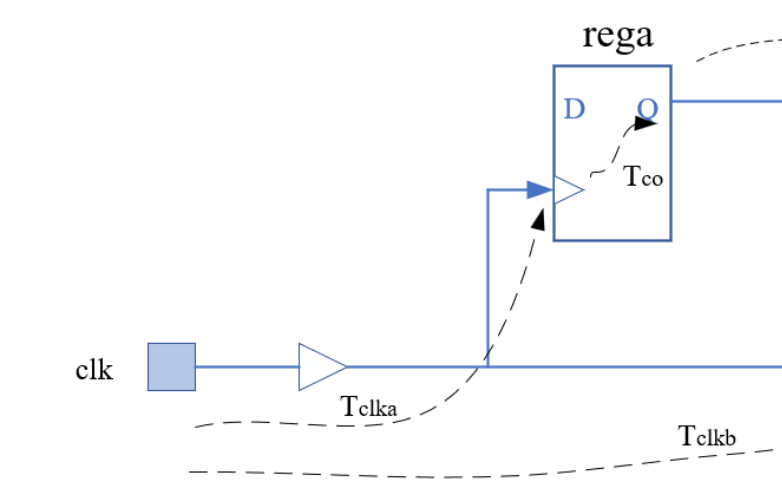

组合逻辑延迟和走线延迟。Tsu表示捕获寄存器建立时间要求。Th表示捕获寄存器保持时间要求。其中Tco、Tsu和Th是由FPGA的芯片工艺决定的。所以,我们所谓的时序约束,实际上就是对

2021-01-12 17:31