PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时脉讯号,使高频器件正常工作,如内存的存取资料等。PLL用于振荡器中的反馈技术。 许多电子设备要正常工作,通常需要外部的输入信号与

2017-05-22 09:16

许多通信、仪器仪表和信号采集系统要求能够同时对多个模数转换器(ADC)上的模拟输入信号进行采样。然后,需要处理采样的数据,期望在这些输入之间同步,每个输入都有自己不同的延迟。对于系统设计人员来说,历来是应对低压数字信号(LVDS)和

2022-12-21 14:41

许多通信、仪器仪表和信号采集系统需要通过多个模数转换器(ADC)对多个模拟输入信号进行同时采样。随后,经过采样得到的数据需被处理以实现各个通道的同步,然而他们各自有不同的时延。这一直以来都成为使用LVDS和

2017-11-18 03:03

使用功率分析仪测量数据时,要选择合适的同步源,如果同步源设定不当,测量值有可能不稳定或出现错误,谐波测量模式还要选择合适的PLL源,不少客户经常提出疑惑,同步源和

2015-07-09 10:37

CACHE 的一致性 Cache的一致性有这么几个层面 1. 一个CPU的icache和dcache的同步问题 2. 多个CPU各自的cache同步问题 3. CPU

2023-06-17 10:38

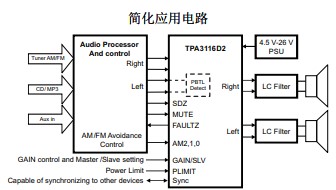

TPA31xxD2高级振荡器/PLL电路采用了一个多开关频率选项来抑制AM干扰;搭配选择使用主从选项时,还可使多个器件实现同步。

2019-06-14 15:41

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的

2023-07-10 10:22

PLL(Phase Locked Loop):为锁相回路或锁相环,用来统一整合时脉讯号,使内存能正确的存取资料。PLL用于振荡器中的反馈技术。许多电子设备要正常工作,通常需要外部的输入信号与内部的振荡信号

2023-05-29 09:51

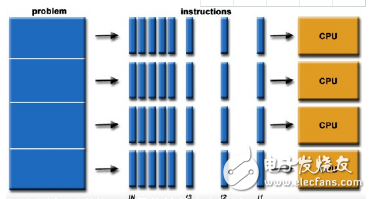

异构并行计算包含两个子概念:异构和并行。 1异构是指异构并行计算需要同时处理多个不同架构的计算平台的问题。 2并行

2018-01-25 16:37