基于FPGA的提取位同步时钟DPLL设计 在数字通信系统中,同步技术是非常重要的,而位

2010-01-25 09:36

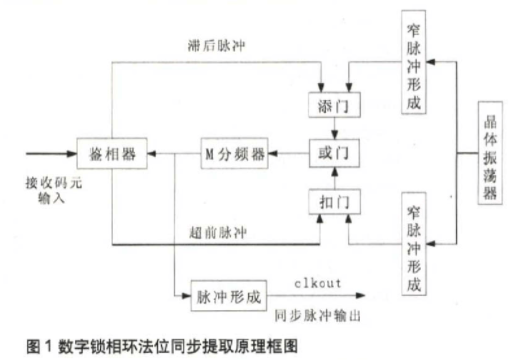

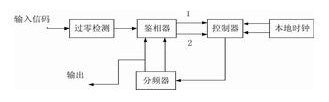

数字锁相环(DPLL)提取位同步信号的原理主要基于相位反馈控制系统,通过不断调整接收端时钟信号的相位,使之与发送端时钟

2024-10-01 15:38

数字锁相环(DPLL)提取位同步信号的设置涉及多个关键步骤和组件的配置。以下是一个概括性的设置流程,以及各个步骤中需要注意的关键点:

2024-10-01 15:41

基于fpga的锁相环位同步提取电路 该电路如图所示,它由双相高频时钟

2010-10-08 12:00

同步信号的提取及行场计数器电路 准确提取视频信号中的

2009-12-08 14:48

正确采样到接收的位流,就需要接收器不断进行重新同步。重新同步表示在位流中每个有效的信号边沿都可对接收信号的时钟周期进行检

2018-03-13 12:53

在数字通信系统中,同步技术是非常重要的,而位同步是最基本的同步。位同步时

2021-05-28 11:20

一般的位同步电路大多采用标准逻辑器件按传统数字系统设计方法构成,具有功耗大,可靠性低的缺点。用FPGA设计电路具有很高的灵活性和可靠性,可以提高集成度和设计速度,增强系统的整体性能。本文给出了一种基于fpga的数字锁相环位

2019-04-19 08:24

位同步,位同步是什么意思 在数字通信系统中,发端按照确定的时间顺序,逐个传输数码脉冲序列中的每个码元。而在接收端必须有准确的抽样判决

2010-03-17 17:31

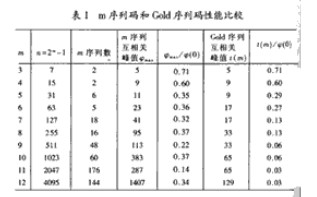

本文介绍一种基于现场可编程门阵列(FPGA)的通信系统同步提取方案的实现。本文只介绍了M序列码作为同步头的实现方案,对于m序列码作为同步头的实现,只要稍微做一下修改,即

2013-04-11 10:53