高速电路传输线效应是指系统工作在50MHz时,将产生传输线效应和信号的完整性问题;而当系统时钟达到120MHz时,则必须使用高速电路设计知识才能使之正常工作。因此,只有

2019-01-22 16:17

如何减少传输线效应 高速电路传输线效应是指系统工作在50MHz时,将产生传输线

2009-04-07 22:34

传输线效应详解 基于上述定义的传输线模型,归纳起来,传输线会对整个电路设计带来以下效应。• 反射信号Ref

2009-03-25 11:29

避免传输线效应的方法针对上述传输线问题所引入的影响,我们从以下几方面谈谈控制这些影响的方法。 6.1 严格控制关键网线的走线长

2009-03-25 11:30

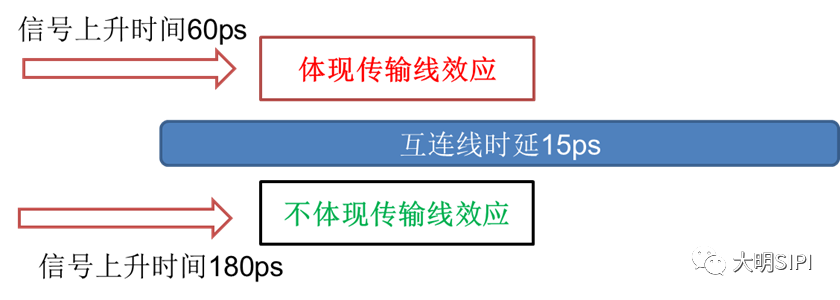

当互连线的长度大于1/6倍的信号上升时间的空间延伸时,互连线就体现出传输线效应。” 上升时间越小越容易体现传输线效应。

2023-06-14 17:06

要解决这些影响PCB信号传输完整性的问题,这就需要工程师采取的一些应对措施。电源层对电流方向不限制,返回线可沿着最小阻抗即与信号线最接近的路径走。这就可能使电流回路最小,而这将是高速系统首选的方法。但是电源层不排除线

2018-11-14 10:38

高速电路传输线效应分析与处理 随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总

2009-11-17 13:57

如何避免高速PCB设计中传输线效应 1、抑止电磁干扰的方法 很好地解决信号完整性问题将改善PCB板的电磁兼容性(EMC)。其中非常重要的是保证PCB板有很好的接

2009-11-20 11:17

解决传输线效应的另一个方法是选择正确的布线路径和终端拓扑结构。走线的拓扑结构是指一根网线的布线顺序及布线结构。当使用高速逻辑器件时,除非走线分支长度保持很短,否则边沿快

2019-06-06 14:55

的焊球上监视SERDES发送器输出信号很难做到。通常信号会引到SMA或SMP连接器后再用示波 器进行监测。然而,信号特性会因为IC和连接器之间的传输线而发生改变。因此,真正的挑战是在SERDES引脚处监视信号性能,而这可以通过去除传输线

2022-11-12 15:14