高速电路传输线效应是指系统工作在50MHz时,将产生传输线效应和信号的完整性问题;而当系统时钟达到120MHz时,则必须使用高速电路设计知识才能使之正常工作。因此,只有

2019-01-22 16:17

如何减少传输线效应 高速电路传输线效应是指系统工作在50MHz时,将产生传输线

2009-04-07 22:34

传输线效应PCB 板上的走线可等效为下图所示的串联和并联的电容、电阻和电感结构。串联电阻的典型值0.25-0.55 ohms/foot,因为绝缘层的缘故,并联电阻阻值通常很高。将寄生电阻、电容和电感

2009-06-18 07:53

传输线效应详解 基于上述定义的传输线模型,归纳起来,传输线会对整个电路设计带来以下效应。• 反射信号Ref

2009-03-25 11:29

避免传输线效应的方法针对上述传输线问题所引入的影响,我们从以下几方面谈谈控制这些影响的方法。 6.1 严格控制关键网线的走线长

2009-03-25 11:30

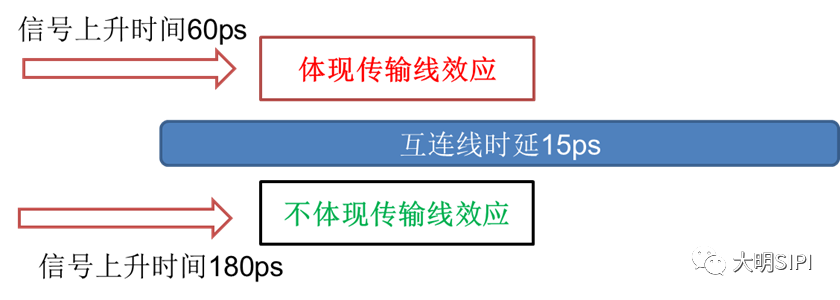

当互连线的长度大于1/6倍的信号上升时间的空间延伸时,互连线就体现出传输线效应。” 上升时间越小越容易体现传输线效应。

2023-06-14 17:06

本帖最后由 eehome 于 2013-1-5 09:56 编辑 http://wenku.baidu.com/view/62cbf7f4f61fb7360b4c650b.html

2012-09-02 09:33

传输线效应的问题。现在普遍使用的很高时钟频率的快速集成电路芯片更是存在这样的问题。解决这个问题有一些基本原则:如果采用CMOS或TTL电路进行设计,工作频率小于10MHz,布线长度应不大于7英寸。工作频率

2017-06-08 15:43

要解决这些影响PCB信号传输完整性的问题,这就需要工程师采取的一些应对措施。电源层对电流方向不限制,返回线可沿着最小阻抗即与信号线最接近的路径走。这就可能使电流回路最小,而这将是高速系统首选的方法。但是电源层不排除线

2018-11-14 10:38

在高速PCB设计过程中,由于存在传输线效应,会导致一些一些信号完整性的问题,如何应对呢?

2021-03-02 06:08